本论文作者王治海是中国科学技术大学 2020 级硕博连读生,师从王杰教授,主要研究方向为强化学习与学习优化理论及方法、人工智能驱动的芯片设计等。他曾以第一作者在 TPAMI、ICML、NeurIPS、ICLR、AAAI 等顶级期刊与会议上发表论文七篇,一篇入选 ICML 亮点论文(前3.5%),曾获华为优秀实习生(5/400+)、两次国家奖学金(2017和2024)等荣誉。

近日,中科大王杰教授团队(MIRA Lab)和华为诺亚方舟实验室(Huawei Noah's Ark Lab)联合提出了可生成具有成千上万节点规模的神经电路生成与优化框架,具备高扩展性和高可解释性,这为新一代芯片电路逻辑综合工具奠定了重要基础。论文发表在 CCF-A 类人工智能顶级会议 Neural Information Processing Systems(NeurIPS 2024)。

- 论文标题:Towards Next-Generation Logic Synthesis: A Scalable Neural Circuit Generation Framework

- 论文地址:https://neurips.cc/virtual/2024/poster/94631

论文概览

逻辑综合(Logic Synthesis, LS)是芯片设计流程中承上启下的关键环节,对芯片设计的效率和质量都具有重要影响。具体来说,逻辑综合旨在生成精准满足给定功能要求(如由电路输入输出对构成的功能真值表)的最优逻辑电路图,是 NP 难问题。为了求解该问题,传统方法主要依赖于硬编码启发式规则,易陷入次优解。

该框架能够精确生成达1200节点规模的电路,该方案为新一代芯片电路逻辑综合工具提供了可行思路与奠定了关键基础。相关技术和能力已整合入华为自研EDA工具。

引言

芯片电路生成的目标是在给定电路功能描述的条件下,生成精准满足电路功能要求且节点数少的逻辑电路图。传统的电路生成方法将高级电路描述语言直接转译为冗余度较高的逻辑电路,这给后续的电路优化带来了较大压力。近期,一些研究通过引入机器学习方法,将电路生成与优化过程有机结合,展现了新一代逻辑综合技术的美好前景。

神经网络架构搜索(Differential Neural Network Architecture Search, DNAS)是一种利用梯度下降法搜索离散结构的技术。已有研究将其应用于生成低冗余电路,展现出了显著的潜力。然而,作者发现现有方法在生成电路时,尤其是在处理大规模电路时,难以实现完全准确的生成,且其性能对超参数极为敏感。

在深入的实验分析后,作者进一步总结出将 DNAS 应用于电路生成的三个主要难点:

- DNAS 倾向于生成大量的跨层连接,导致网络表达能力受限。

- 神经网络结构与电路固有结构存在较大偏差,显著降低了 DNAS 的搜索效率。

- 不同输入输出示例数据的学习难度差异显著,现有方法难以学习难例输入输出对。

为系统性地解决这些挑战,作者提出了一种新颖的正则化三角形电路网络生成框架(T-Net),实现了完全准确且可扩展的电路生成。此外,他们还提出了一种由强化学习辅助的演化算法,以实现高效且有效的电路优化。在四个电路评测标准数据集中,实验表明他们的方法能够精确生成多达 1200 节点规模的电路,且其性能显著优于国际逻辑综合竞赛 IWLS 2022 和 2023 中冠亚军方案。

背景与问题介绍

逻辑电路生成介绍

逻辑电路图(And-Inverter Graph, AIG)是逻辑电路的一种表示方式。AIG 为有向无环图,图中的节点代表与逻辑门,图中的边代表逻辑门间的连线,连线上可以添加非门。逻辑电路的大小为 AIG 中的节点数,在逻辑功能不变的情况下,节点数越少表示电路结构越紧凑,这将有助于后续的芯片设计优化。

逻辑电路生成方法将电路的完整输入输出对组合,即功能真值表,建模为训练数据集,并利用机器学习模型自动从数据集中学习生成逻辑电路图 [1,2,3]。在电路设计的实际应用中,要求设计精准满足功能要求的电路结构,因此生成的逻辑电路图必须在训练集上达到 100% 的准确率。

基于 DNAS 的电路生成介绍

神经网络架构搜索(Differential Neural Network Architecture Search, DNAS)[4] 近期被用于生成逻辑电路图 [2,3]。这类方法将一个 L 层,每层 K 个神经元的神经网络建模为 AIG,其中神经元视为逻辑门,神经元之间的连接视为逻辑门之间的电路连接,神经元可以连接到更浅层的任意神经元。对于一个参数化的神经网络,每个神经元都固定执行与逻辑运算,而神经元之间的连接参数是可学习的。

为了能够使用梯度下降法训练网络结构,现有方法会执行 2 种连续化操作:1. 神经元的逻辑运算用等价的可微方式计算,例如 a 与 b 用 a⋅b 代替 [5]。2. 将离散的网络连接方式参数化,并在前向传播时使用 gumbel-softmax [6] 对连接进行连续化和采样。

在训练期间,真值表的每一行输入 - 输出对都作为训练数据输入网络,通过梯度下降法训练连接参数。在测试期间,每个节点的输入根据参数只选择一条连接,从而将网络离散化,模拟实际的逻辑电路。

动机实验 ——DNAS 难以准确生成电路

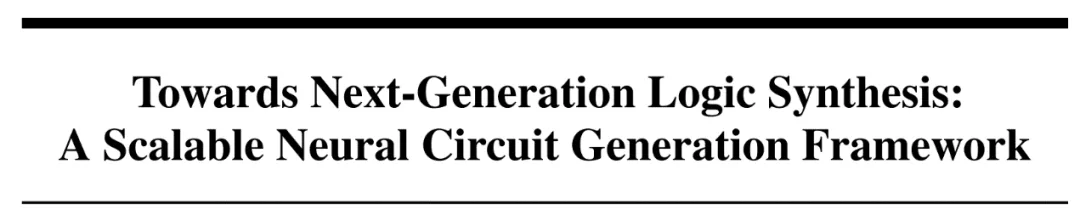

作者使用上述 DNAS 方法生成电路,生成准确率和电路的规模如图 1(a)所示。结果显示,现有方法难以准确生成电路,且准确率随着电路规模增大而减小。同时,他们发现生成准确率对网络初始化方式及其敏感,方法的鲁棒性较差。

图 1. 观察实验。(a) 现有的 DNAS 方法难以准确生成电路,特别是大规模电路。(b) 输出节点位于网络浅层,跳过了大量可用节点。(c) 实际只有约四分之一的节点被使用 (深色)。(d) 电路各层节点数统计,与普遍使用的方形网络存在差异。

为了进一步分析产生上述挑战的原因,作者进行了详细的实验。

首先,他们发现网络利用率很低。由于节点间的连接可以跨层,因此存在被跳过的节点。图 1(b)展示了经过训练后输出节点位于网络中的位置,可以看到大部分网络层都被跳过,没有连接进最终电路。图 1(c)展示了网络中实际使用到的节点(深色),只有约四分之一的底层节点被使用。过度的跨层连接浪费了大量网络结构,限制了网络的表达能力。

接着,他们发现实际电路结构与网络之间存在结构偏差。他们统计了使用传统方法生成电路的各层节点数,如图 1(d)所示。图中展示了实际电路在底层有着更多节点,而顶层则节点更少,这与普遍使用的方形网络存在差异。

最后,他们发现不同输入 - 输出示例之间存在学习难度差。具体来说,它们在训练时的 loss 收敛速度存在显著差异。这与通常认为的独立同分布(IID)假设并不相同。更多细节可见原论文第 4 章节。

方法介绍

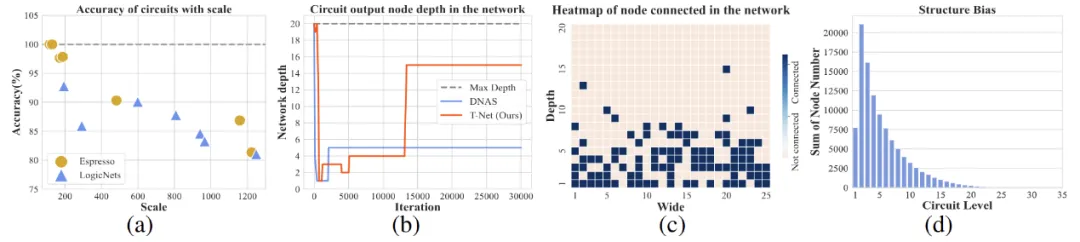

针对以上三个挑战,作者设计了新颖的正则化三角形电路生成框架(T-Net),如图 2 所示。它包含 3 个部分:多标签数据变换、三角形网络结构、正则化损失函数。

图 2. 作者提出的电路生成框架图,包含多标签数据变换、三角形网络结构、正则化损失函数三部分。

多标签数据变换:提高可扩展性

随着输入位数的增多,真值表的长度呈指数型增长。为了解决扩展性挑战,作者设计了基于香农定理的多标签训练数据变换。香浓定理证明了一个逻辑函数可以通过一个分解变量分解成两个子函数:

由于真值表是逻辑函数的对偶表示,他们通过以下两步完成数据变换:首先选定一个输入变量,通过固定它的值为 0 或 1,将真值表分解为 2 个长度减半的子表。接着将 2 个子表并列起来,每个输入组合的输出数量翻倍。

通过将真值表合并生成,网络可以学习到更多可复用的结构,从而减少最终的电路节点数。多标签数据变换可以不断减少真值表的输入位数,从而降低学习难度,加速电路生成。

三角形网络结构:减小搜索空间

为了使网络结构更好地适配电路特性,作者设计了三角形的网络结构。具体来说,更宽的底层结构增强了网络的表达能力,而细长的顶层结构减少了利用率低的冗余节点,减小了搜索空间,加速了收敛。同时,实验证明了这种窄顶结构也能有效加速具有大量输出的电路生成。

正则化损失函数:精确生成电路

本论文的方法包含跨层连接正则化和布尔难度识别损失函数两部分。对于跨层连接,作者对可学习的连接分布参数施加权重正则化,鼓励网络连接更临近层的节点。对于较难学习的输入 - 输出示例,他们在损失函数中为这些示例施加更大的权重,以在训练后期加速收敛。

同时,本论文的框架还包含电路优化部分。作者在强化学习优化算子序列调优的基础上,结合了演化算法和 agent 重启技术,避免陷入局部最优解,实现快速有效的电路优化。更多细节可见原文第 5 章节。

实验介绍

本论文实验的数据集包括 4 类开源电路数据集,节点数规模高达 1200,输入、输出数量最高为 16、63 位。

实验包含 4 个部分:1. 在多个电路上评估本论文电路生成和优化方法的准确性和电路性能。2. 评估本论文生成方法针对电路大小的可扩展性。3. 通过消融实验展示本论文方法各部分的效用。4. 验证本论文方法对超参数的鲁棒性。

作者在以下内容中详细介绍实验 1,其余实验请参见原论文的第 6 章节。

电路生成准确率

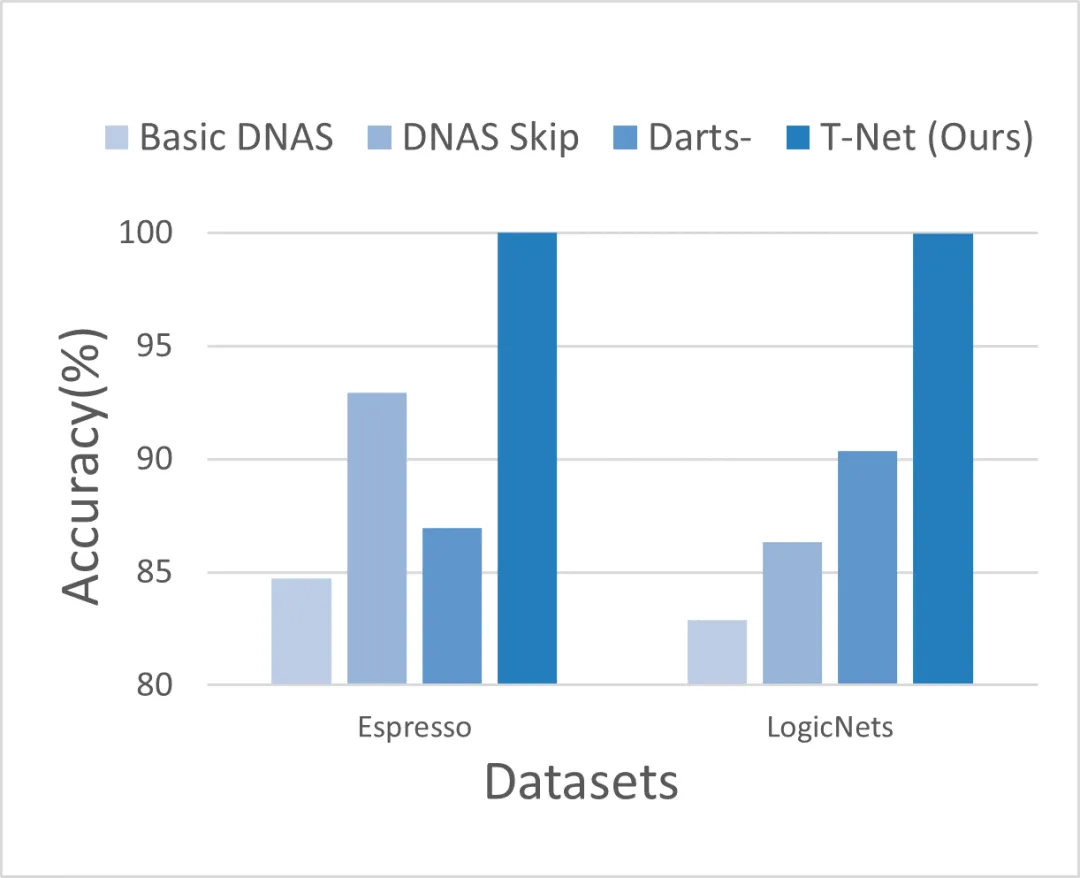

部分实验结果见图 3,作者在开源电路上对比了他们的方法与其他基于 DNAS 生成方法的准确率。实验结果显示,他们的方法准确率大幅提升,并可准确生成 1200 节点规模的电路。

图 3. 作者提出的 T-Net 相比其他 DNAS 电路生成方法准确率大幅提升。

电路综合效果

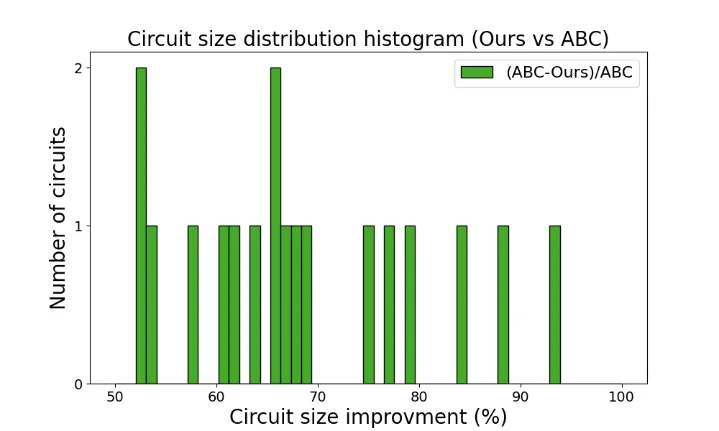

部分实验结果见图 4,作者在开源比赛电路上对比了他们的方法与开源逻辑综合工具 ABC 和 IWLS 比赛冠亚军的电路大小。实验结果显示,他们的方法显著优于开源逻辑综合工具 ABC 中的电路生成算子,且超过了 2022 和 2023 年比赛冠亚军的方案。

图 4. 作者提出的电路生成及优化框架效果显著优于开源逻辑综合工具 ABC 中的电路生成算子。