我随手找到的一个 CPU 型号 Intel(R) Xeon(R) Platinum 8260 CPU。这个 CPU 型号中的各段数字分别都代表的是什么含义,从中我们可以得到哪些有价值的信息。让我们带着这个型号进入到今天的服务器 CPU 原理解读。

服务器 CPU 市场上目前虽然有 arm 和 RISV-V 架构入场,但最主流的品牌目前仍然还是 x86 架构,厂家主要还是 Intel 和 AMD 两家。

其中 Intel 针对服务器市场推出的子品牌型号是 Xeon。我们今天主要围绕 Intel 的 Xeon CPU 来展开介绍。

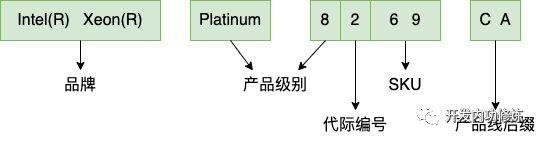

图片

图片

第一部分是品牌标志。Intel(R) Xeon(R) 表示的是这是 Intel 的 Xeon 服务器 CPU。第二部分是 CPU 级别。Intel 在 2017 年之前对服务器 CPU 是使用 E3、E5 和 E7 的方式来命名。其中 E3 代表的是入门级别的服务器处理器、E5 代表中端、E7代表高端。这种命名方式类似于桌面处理器中的 i3、i5 和 i7,数字越大代表的档次越高。但在 2017 年之后,开始使用 Platinum(铂金)、Gold(金牌)、Silver(银牌)。

另外代表级别的字符串如 Platinum 和后面的第一位数字是有对应关系的,

如果数字是 8、9 都代表的是 Platinum 系列,定位高端

如果数字是 6、5 都代表的是 Gold 系列,定位中端

如果数字是 4 代表的是 Silver 银牌系列,定位入门级服务器 CPU

第三部分的一位数字代表的是 CPU 的代际。这是 2017 年之后开始的可扩展处理器家族代际标识。其中数字越大代表 CPU 架构越新。

- 1 代表第一代可扩展处理器,对应代号 Skylake(2017 年发布) 的架构设计

- 2 代表第二代可扩展处理器,对应代号 Cascade Lake(2019 年发布) 和 Casecade Lake-R(2020 年发布) 的架构设计

- 3 代表第三代可扩展处理器,对应代号 Cooper Lake(2020 年发布) 和 Ice Lake(2021 年发布)的架构设计

- 4 代表第四代可扩展处理器,对应代号 Sapphire Rapids(2023 年发布)的架构设计

第四部分是 SKU 编号。这是 CPU 厂商为了方便对所有的产品进行库存管理而制定的编号。这类似于超市里商品的条形码、图书的 ISBN 号,方便查询和管理产品的库存量。一般来说,这个值也是越大性能越好,但不绝对。

第五部分是产品线后缀。其中 C 代表单 CPU 插槽。Q 代表支持液冷。N 代表的是针对通信/网络/NFV 网络功能虚拟化优化。T 代表的是根据长寿命使用要求设计的能满足 10 年使用周期支持。P 代表针对 IaaS 云环境优化。V 代表针对 Saas 云环境优化。

二、服务器 CPU 代际简介

服务器 CPU 的代际发展和 PC 家用 CPU 的过程基本上是一致的,但在命名方式上有所不一样。服务器 CPU 的代际从 2017 的 Skylake 开始,命名为了第一代可扩展处理器。接下来的代际命名都是在这个基础之上更新。

时间 | 代数 | CPU代际 | 制程工艺 | 微架构 |

2017 | 第1代 | Skylake(server) | 14nm | Skylake |

2019 | 第2代 | Cascade Lake | 14nm | Skylake |

2020 | 第3代 | Cooper Lake | 14nm | Skylake |

2021 | 第3代 | Ice Lake(server) | 10nm | Sunny Cove |

2023 | 第4代 | Sapphire Rapids | 7nm | Golden Cove |

其中我们开头提到的 8260 是属于第二代,2019 年发布,对应代号 Cascade Lake。

图片

图片

在第二代可扩展处理器这个代际中,采用的是 14nm 工艺。该代际既包括服务器 CPU,也包括个人 PC CPU。对于个人 PC CPU,是归属到酷睿 i7 和 i9 等型号中。对于服务器是归属到 Xeon Platinum(铂金)、Xeon Gold(金牌)、Xeon Silver(银牌)、Xeon Bronze(铜牌)。

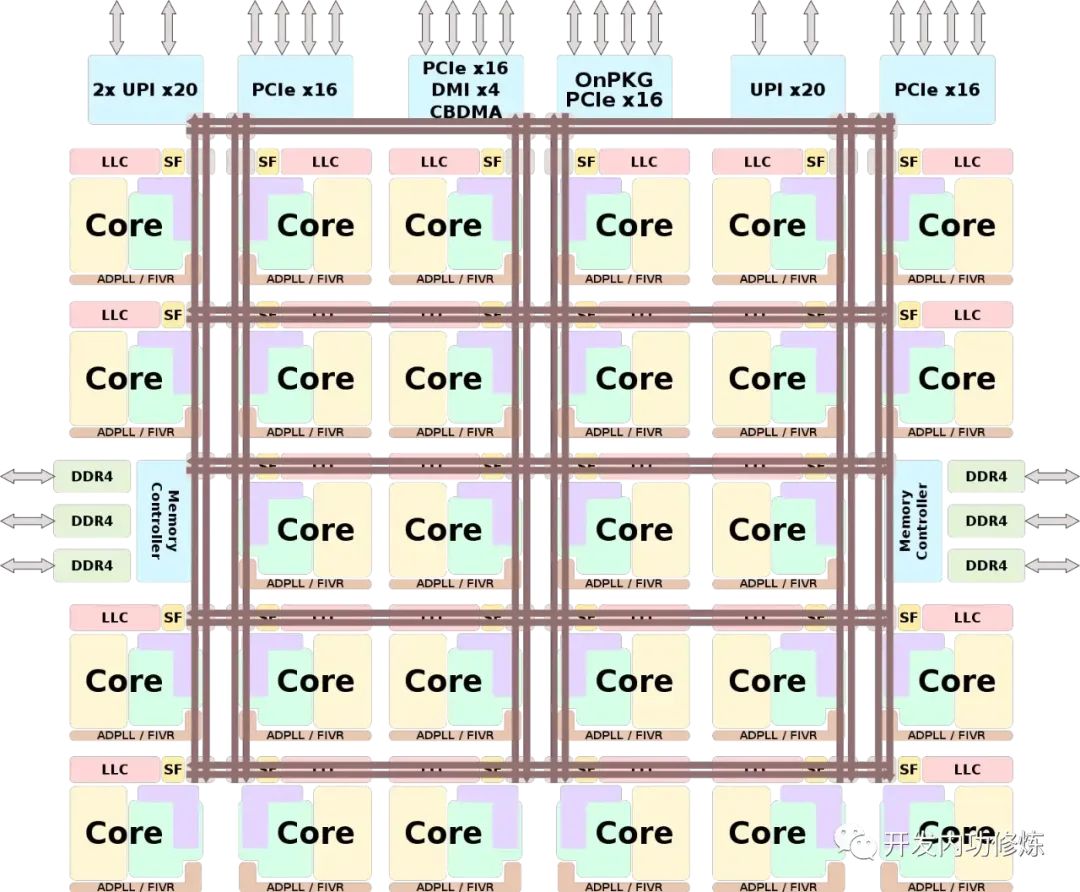

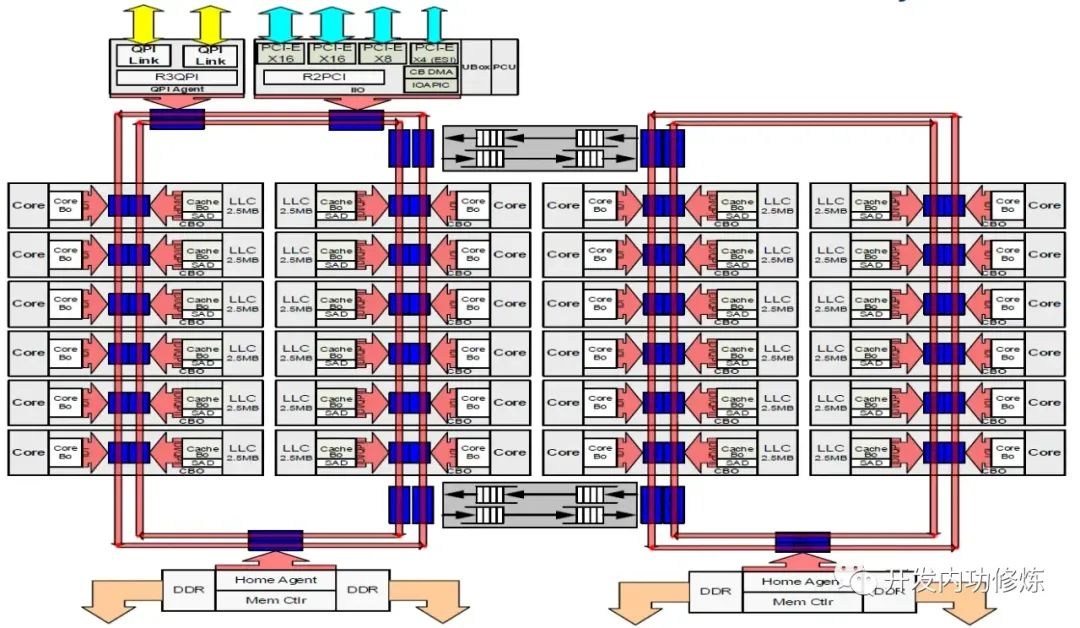

其中在 Xeon Platinum(铂金)系列中,最高可以支持到 28 个物理核心。核更多是和个人 PC CPU 中最大的不同点。下图是 28 物理核 CPU 芯片的系统结构如下。

图片

图片

主要分成三个大部分。

第一个大部分是 IMC(integrated memory controller)内存控制器。

就是上图中的 Memory Controller。Cascade Lake 支持的服务器内存规格是 DDR4 2933 MHz。从图中可见有该 CPU 两个内存控制器模块,每个内存控制器都可以支持 3 个内存通道(channels),每个通道可以插两个 DIMM 内存条,总共支持最大插 2*3*2 = 12 个内存条。

第二个大部分就是各个物理核了。

这个代际中采用的是 Mesh 架构。在 Mesh 架构中,把所有的物理就是把所有的物理核按照行、列的二维的结构进行排列。关于 Mesh 架构后面我们在第四小节中介绍。

在每个核上方的 LLC 是我们常说的 L3 级缓存,其实 LLC 是末级缓存 (Last Level Cache)的意思,叫法更为准确一些。值得注意的是,虽然 LLC 是分成了在每个核上都有一块,但整个 CPU 上的所有 LLC 都是共享的。

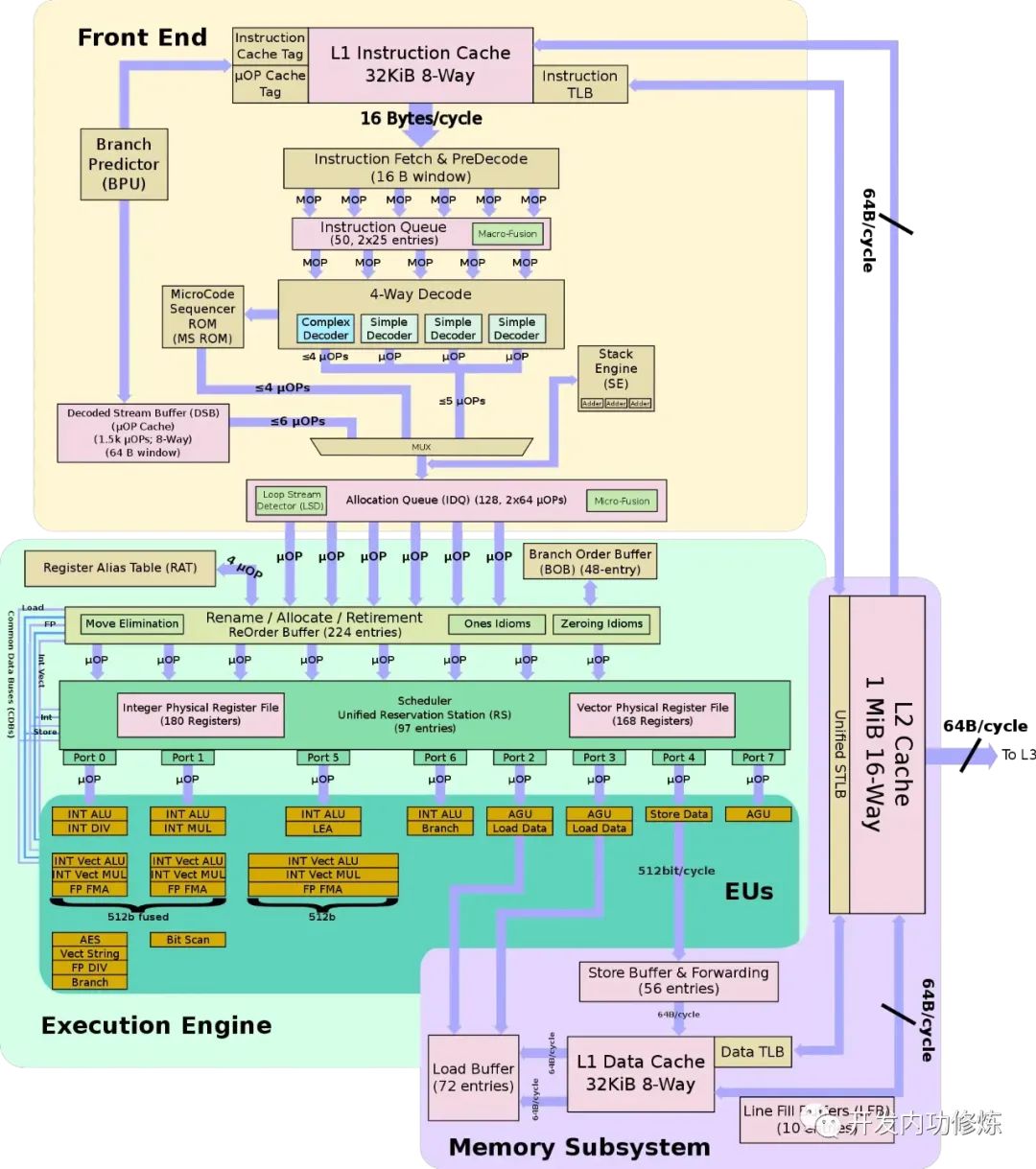

每个物理核的内部就和个人 PC CPU 中的核一样,都是采用的 Skylake 微处理器架构设计的。每个物理核有 32 KiB 的 L1 指令缓存、32 KiB 的 L1 数据缓存、1 MiB 的 L2 缓存。更详细的 Skylake 微处理器架构图如下。

图片

图片

第三个大部分是 Notrh Cap 部分。

这个部分包含 PCIe 总线(用来连接显卡硬盘等)和 UPI 总线(用于多 CPU 片间互联)。

关于 PCIe 总线,我们在个人 CPU 的型号、代际架构与微架构 中提到过。它是一种用于连接高速组件的高速串行计算机扩展总线标准。第二代 Cascade Lake 支持的是 PCIe 3.0 标准,单通道速率为 8 GT/s (984.6 MB/s)。用来连接显卡或者固态硬盘等高速设备。

UPI 总线是用于多 CPU 片间互联使用的。Xeon Platinum 系列 CPU 支持 3 个 UPI 连接。而低端的 Xeon Gold 5xxx、Xeon Silver 等只支持 2 个 UPI。关于 UPI 后面我们再单独说。

三、片内总线之 Mesh 多核架构

在服务器 CPU 架构设计中,要解决的关键问题是如何合理设计多核布局,以更低的延迟实现对内存的访问。所以,片内也需要“总线”进行互联。

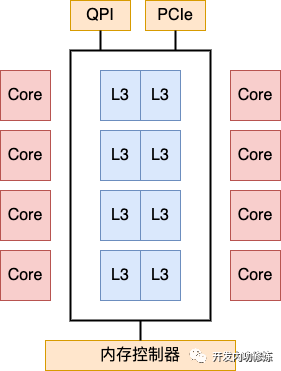

在 2017 年的 Skylake 之前,Intel 采样的方式是环状互联,也叫 Ring 架构。在 Ring 架构里,所有的核都用一个环来连接。每个核需要访问内存的时候,都通过这个这个环来进行。

大家都知道,后来服务器的发展都是朝着多 CPU 核的方向在发展。随着时间的推进,核数越来越多。传统的 Ring 架构的环状结构中,核越多,环就越大,核通过环来访问内存数据时延迟就会越大。

图片

图片

为了降低环上核的数量,Intel 还曾在高端 CPU 中为了塞进更多的核,设计了个双环结构。这样,环上的核就少了,数据传输路径就短了一些。

图片

图片

但即便是分成了两个环,依旧会有核心越多延迟越大的问题,且跨环访问时会增加一个额外的 CPU cycle 的延迟,所以 Broadwell 算是把 Ring 架构续命做到了极致最多也只塞到了 24 个核心。

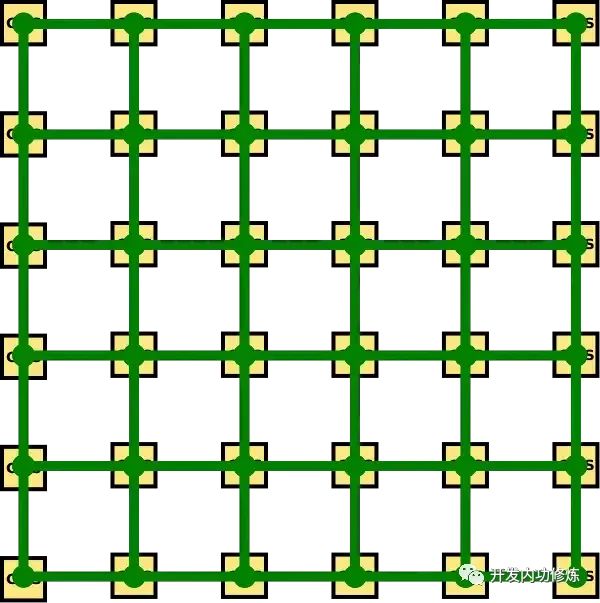

所以为了更好地控制多核处理器访问内存时的延迟。Intel 于 2017 年推出的 Skylake 中采用了 Mesh 架构来设计多核处理器。所谓 Mesh 架构,就是把所有的物理核按照行、列的二维的结构进行排列 。

在最高规格的 28 个物理核的芯片设计中,采用了 5 行 6 列的矩阵结构。其中 2 个位置用于放上面提到的内存控制器。接下来的每个位置都放了一个物理核。

Ring 架构演进到 Mesh 架构后,片内总线也从一维结构演变到了二维结构

图片

图片

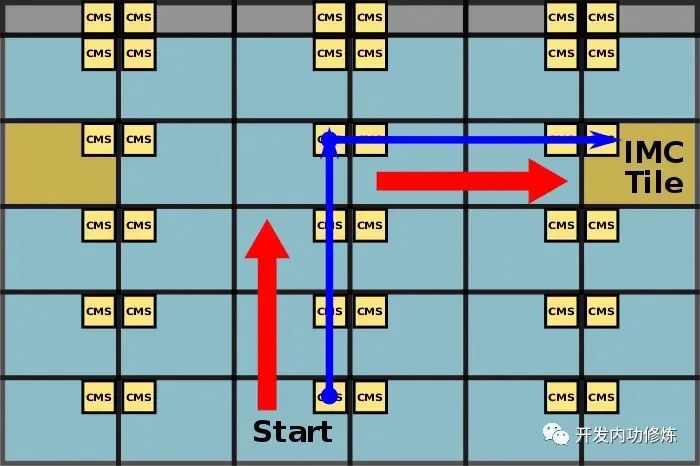

这样,当某个物理核在访问内存数据的时候,就可以通过这个二维结构找到一个最短路径来通信了。例如下图中 Start 这个位置的核想要访问内存,这时候的访问路径是先沿着红色箭头向上,然后再沿着另一个红色箭头向右到达内存控制器来访问内存。

图片

图片

有了这个二维结构后,访问内存的路径就会低一些,也就为在低延迟的情况下设计更多的物理核提供了可能。在 Cascade Lake 代际下设计到了 28 个物理核。

图片

图片

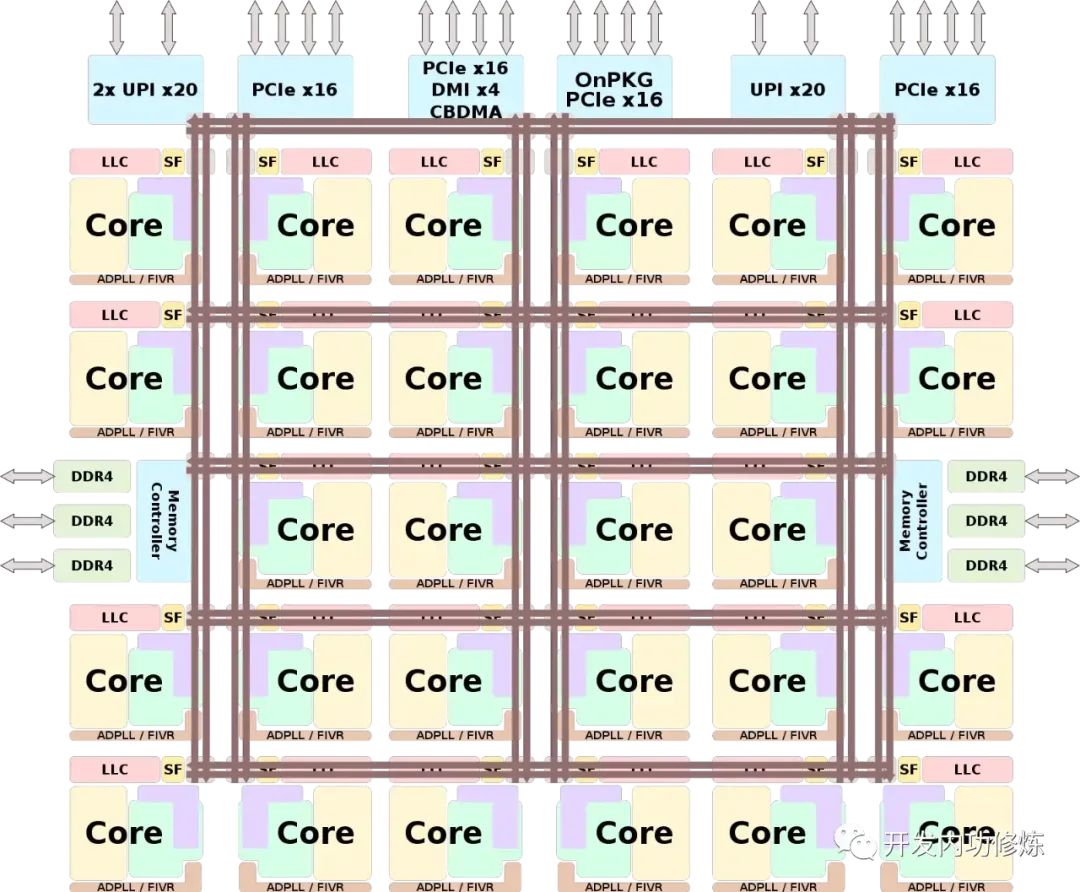

后面的服务器 CPU 仍然还延续使用 Mesh 架构,在 2021 年发布的 ice lake 中,更是设计到了 7 行 8 列的矩阵结构,共放了 40 个物理核。

关于更多 Mesh 架构的介绍参见 https://en.wikichip.org/wiki/intel/mesh_interconnect_architecture

四、片间总线之 UPI 多处理器互联

单个 CPU 即使用尽全力,能设计进去的物理核仍然是有限的。所以另外一个计算扩展思路是多处理器互联,在一台服务器上安装多个物理 CPU,进而达到扩展算力的目的。

前面我们看到,每个 CPU 都是支持多条内存的,都可以通过内存控制器和自己的内存插槽上的内存进行通信。但现代的服务器一般都不只是一个 CPU。这样问题就来了,A CPU 如何访问另外一个 CPU 插槽上内存里的数据。

答案就是 UPI 总线,它是 Ultra Path Interconnect 的简称。

在 17 年之前的服务器 CPU 中,采用的是 QPI(QuickPath Interconnect) 总线进行 CPU 之间的互联。从 2017 年的第一代可扩展处理器开始,Intel 就采用了更为快速的 UPI(Ultra Path Interconnect) 总线。UPI 总线相对于 QPI 总线,传输速度更快,从9.6 GT/s 提升到了 10.4 GT/s,而且功耗还更低。

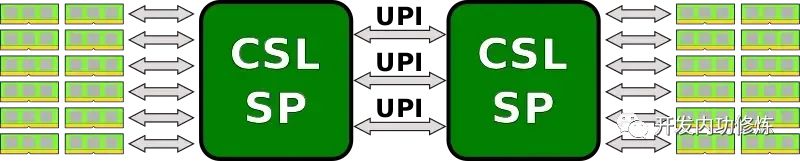

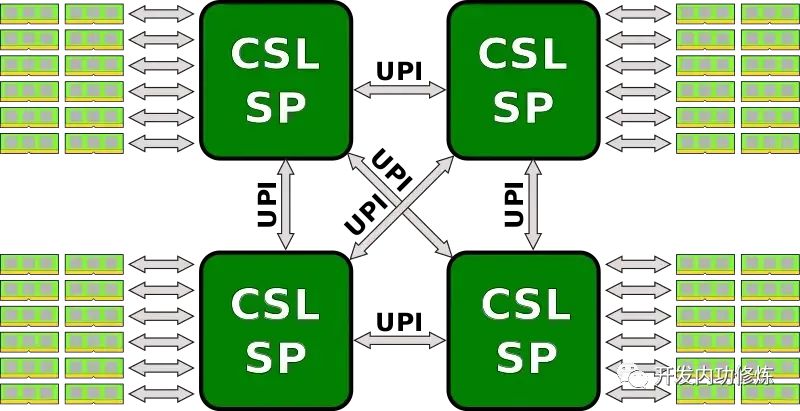

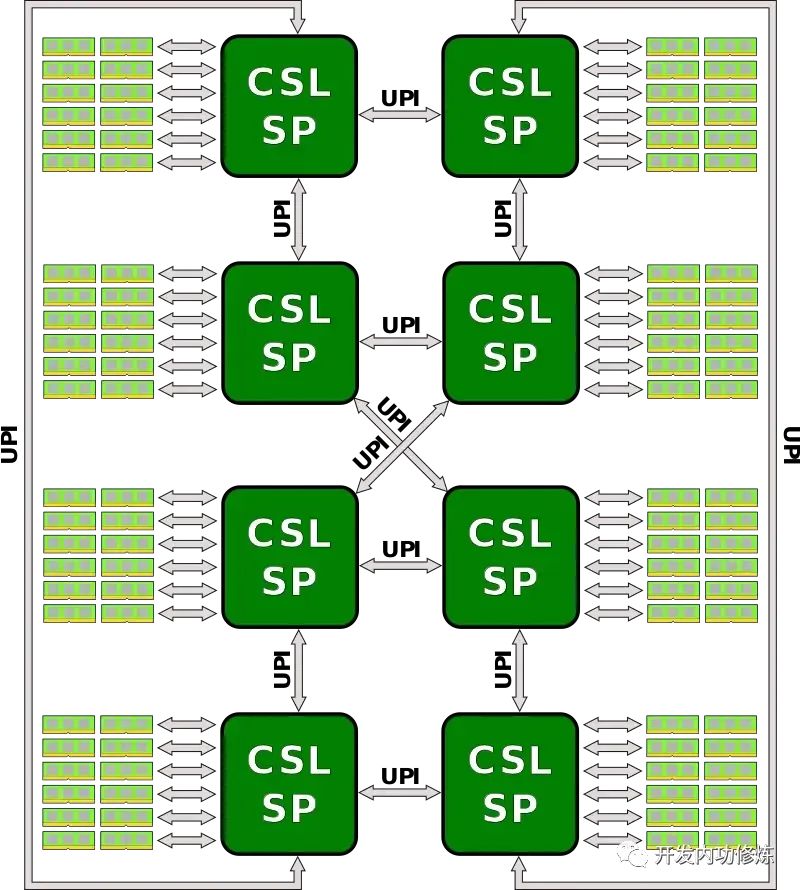

通过 UPI,可以实现双处理器、四处理器、甚至是八处理器之间的互联。Xeon Platinum 都支持 3 UPI 连接。对于 Xeon Platinum 系列,双处理器的连接方式如下

图片

图片

四处理器的连接方式如下

八处理器的连接方式如下

Intel 通过 UPI 总线,极大地提高了多处理器可扩展性。不过虽然 Intel 支持最多八处理器,业界线上使用的最多的仍然是双处理器的 UPI 互联。

总结

在本节中,我们以较为常用的 Intel(R) Xeon(R) Platinum 8260 型号的 CPU 作为引子,对服务器 CPU 的型号命名规范、各个代际的发展过程、以及片内总线之 Mesh 架构、片间 UPI 总线互联。

Intel 的服务器 CPU 从 2017 年开始后采用了新的代际命名规范。2017 年的 skylake 作为第一代,目前到了第四代。在每一代中,Platinum 都是最高端的 CPU 型号、接下来依次是 Gold、Silver。

其中 8260 是属于第二代可扩展 CPU,代际代号为 Cascade Lake。我们找到了它的芯片结构图。主要包括内存控制器、各个物理核、PCIe总线、UPI总线等部分。

为了更好地在低延迟的情况下实现更多的物理核,8260 采用的 Mesh 架构来组织所有的物理核。在 Mesh 架构中,把所有的物理就是把所有的物理核按照行、列的二维的结构进行排列。能较为有效地控制物理核访问内存时的延迟。

除了片内设计更多的物理 CPU 的思路外,另外一个扩展算力的方法是在一台服务器内设计多个 CPU。而多个 CPU 之间是通过 UPI 总线进行互联的。通过该总线,单服务器最多可以实现八颗 CPU 的互联。