1.介绍

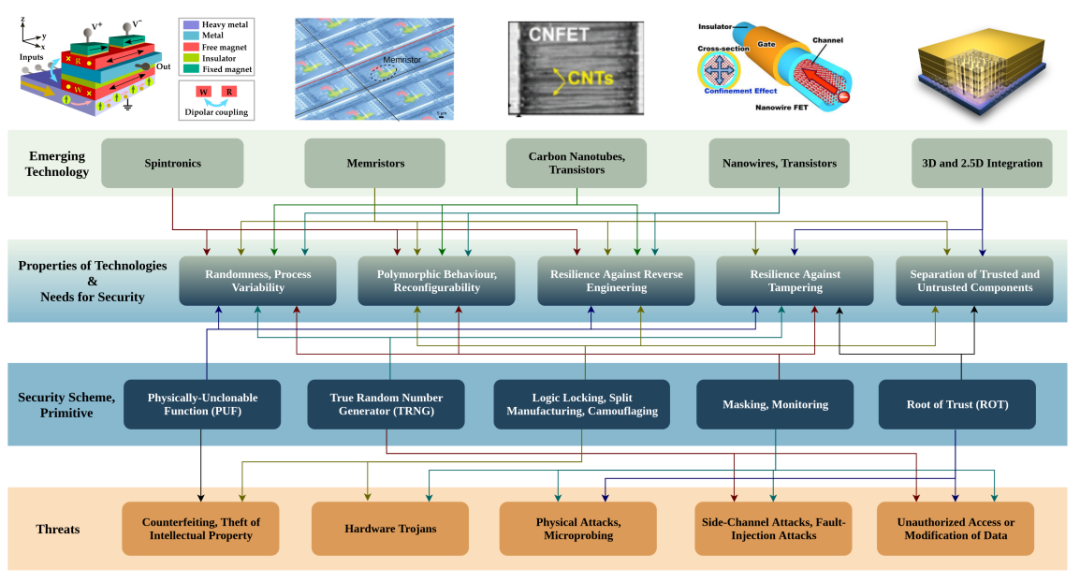

图1展现了本文所涉及的新兴硬件安全技术、以及新兴硬件安全技术中与硬件安全相关的和有利于硬件安全的特性、相应的安全方案以及这些方案所应对的安全威胁。

图片

图片

2.新兴器件

新兴器件有一些共同的有趣特性,这些特性是传统CMOS技术难以实现的。更具体地说,自旋电子学、忆电阻器、碳纳米管晶体管和NWFET都可以定制,以包含显著的可变性、随机性、可重构性、多态行为、反逆向工程的弹性,也可能用于分离可信和不可信部件(后者通过分裂制造的方式)。因此,这些器件可以很好地服务于puf、trng、IP保护方案,并屏蔽侧通道泄漏。此外,忆阻器还可以通过破坏性数据管理提供抗篡改的弹性。

这种基于新兴器件的安全方案的实际实施前景取决于各个方面,从一般的电路设计和安全分析,到制造能力和设备成熟度等等。其他论文也回顾了硬件安全背景下的新兴器件,例如,详见[1-3]。

2.1 自旋电子学

当前各种研究都提出了IP保护的多态行为和/或可重构性。例如,Alasad 等人[4]使用全自旋逻辑进行伪装。然而,他们提出了一些设备独特的原语布局;在基于图像的逆向工程中很容易区分出来。此外,它们的原语能量消耗相对较高,ns-range延迟大约消耗350uw。在[5]中,作者介绍了针对设计混乱引入了基于自旋电子学的可重构查找表(lut)。然而,这些方法在抗SAT攻击方面可能达不到预期的效果。还要注意,这种方法在概念上类似于利用传统的现场可编程门阵列的设计混淆。在[7]和[6,8]中,分别基于畴壁运动器件和在巨自旋霍尔效应(GSHE)器件研究了多态和模糊逻辑。后一种逻辑研究相对于前一种研究的重要好处是它们的每台设备支持所有16种可能的功能;这使得这些设备在SAT弹性方面优于其他设备。

在[9]中,提出了基于多态电磁自旋轨道(MESO)器件的“动态伪装”的概念。与常规的伪装不同,这种概念也能针对制造厂和测试设施中的“对手”从而起到保护作用,因为真正的功能只在稍后的多态织物中配置。因此,“动态伪装”在概念上也类似于逻辑锁定。然而,与锁定不同的是,实现这种安全性不需要额外的设备或门。

人们注意到自旋电子学可以提供一些抵御侧信道攻击的弹性。例如,这些器件的磁电开关不发射光子;首先可以排除中的相关的攻击。由于自旋电子学用于逻辑、基于磁场或温度曲线的故障注入和侧信道攻击可能更难实现,这与用于记忆的自旋电子学不同。此外,在[10]中,作者使用自旋电子学来构建多态电路和不同的电路模板,在运行时进行随机切换,以屏蔽功率侧信道。

在[11]中,作者提倡在puf的畴壁存储器中制造纳米线的工艺变化。在[12]中,作者利用了trng中纳米磁铁固有的随机自旋开关机制。通过器件级模拟,作者证明了他们的TRNG器件可以在很大的温度范围内工作,不受工艺变化的影响,并且可以以比CMOS TRNG显著更小的布局成本实现。在[13]中,作者提出了一种基于反铁磁的安全内存方案,该方案提供了对篡改、侧通道和读出攻击的保护,并保证了比STT-RAM或pcm更低的位能量。

大多数研究都集中在电路设计和安全性分析上,而对技术方面的研究很少。尽管自旋电子学在应用方面取得了快速进展,但在相关安全研究中考虑技术探索似乎也很重要。

2.2 记忆电阻器

在硬件安全方案中使用忆阻器的潜力在几年前就已被认识到,例如在2013年利用忆阻器的过程变化和随机操作的puf。最近,另一个PUF概念被提出,该概念利用忆阻器的非线性I-V特性(“捏滞”),并应用忆阻电导的模拟调谐,以提高这类PUF的性能和实用性,并降低外围电路的复杂性。[14]的作者为他们的PUF概念提供了实验演示和测量结果。

记忆交叉条数组是密匙安全管理的核心。作者建议将记忆电阻器件的唯一指纹与这些器件内的键值存储相结合。他们构建了控制电路,一旦提取指纹(用于验证芯片的真实性),密钥就会被销毁。因此,秘密密钥在芯片上保持“活性”,以启用其功能(遵循逻辑锁定的概念),直到执行任何读取。作者为他们的概念提供了实验证明和测量结果。这样的概念对于逻辑锁定的实用性来说是重要的一步,它需要防篡改存储器来保证它的安全,以对抗领域中的恶意终端用户。

在[15]中,作者还在忆阻器的背景下提出了用于混淆的多态电路。这是可能的,因为在原则上,在这种模糊逻辑中的忆阻器件的功能可以重新配置。虽然作者提供了电路和布局级别的第一个研究——尽管没有技术探索和库描述的细节——他们没有提供任何实验演示。此外,其他研究对基于忆阻的逻辑的延迟和功耗提出了警告,除非对电路结构进行优化,这似乎与混淆原理相冲突。

2.3 碳纳米管和碳纳米管场效应晶体管

在[16]中,作者提出了利用碳纳米管制造可变性的puf以及洛伦兹混沌系统的概念。后者的作用是增强puf的输入和输出的去相关性,从而使它们更能抵御机器学习攻击。在[17]中,作者对cntfet进行了基于仿真的关于木马检测、电源侧通道泄漏和伪装的研究,发现与传统CMOS技术相比,cntfet在各方面都更有前途。在[2]中,作者综述了CNTS在puf、trng中的应用,并提出该技术可用于检测微探针或其他侵入性攻击的新型传感器。

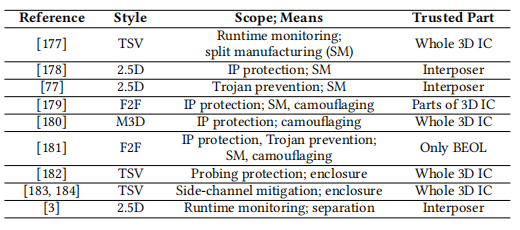

表1:利用2.5D/3D集成提高硬件安全性的精选作品

图片

图片

2.4 碳纳米管和纳米线场效应晶体管

在[18]中,作者提出了用于伪装的硅纳米线场效应晶体管。更具体地说,它们利用nwfet中可控的双极性来建立一个包含NAND、NOR、XOR和XNOR功能的伪装原语。作者还建立了一个多态NAND/NOR门,并给出了电路仿真结果。然而,在[6]中,研究表明这些原语容易受到SAT攻击。

在[19]中,作者首先探讨了如何利用晶体管级可重构性在硅纳米场效应晶体管模型的背景下进行逻辑锁定和分裂制造。其次,他们研究了如何利用可重构性来诱导短路电流或开路配置,从本质上消除芯片的可靠性和功能特性;作者认为,可重构nwfet的这一关键特性可能被恶意利用为以可靠性为中心的木马,也可能被故意利用为“杀死开关”。在[20]中,利用纳米线与等离子子相互作用的光学检测被提出和实验证明。这个想法适用于芯片(或其他商品)的标签和认证。由于不需要纳米线,作者在中提出了等离子体增强光puf的概念,并提供了物理模拟结果和安全性分析。

3. 3D和2.5D集成

3D和2.5D集成为提高硬件安全性提供的主要好处是:组件的物理分离,无论是跨互连、有源设备,还是两者都有;组件的物理外壳,以保护它们免受现场对抗活动的影响。其他论文也回顾了3D和2.5D集成对硬件安全的好处和坏处,例如,详见[21]。

3.1 硬件的机密性和完整性:逻辑锁定

3D和2.5D集成还没有被用于逻辑锁定。在松散相关的工作中,利用锁定原则来推进分离制造的概念。更具体地说,它们锁定FEOL并将解锁工作委托给一个独立的、受信任的BEOL设施。作者指出,他们的方案也可以在包或板级别解锁,这很可能建议作为2.5D IC实现。

3.2 硬件的机密性和完整性:伪装

第一个专门为3D集成提出伪装的人,是针对M3D IC。作者开发并描述了自定义M3D伪装库,并在门级和芯片级评估了他们的方案。

这种伪装是通过虚拟接触来实现的,在经典二维集成电路中这种方法已经被提出。因此,虽然在概念上并不新鲜,但[22]中的工作利用了M3D集成电路提供的好处,以努力提高伪装的可伸缩性。这是值得注意的,因为现有技术的伪装可能会产生相当大的布局成本。实际上,这样的成本只考虑到少数被伪装的大门;而有限的伪装尺度又使此类方案容易受到SAT攻击。相比之下,[22]报告的工作与常规2D门相比,平均只消耗25%的电力,15%的延迟成本,43%的面积节省。

3.3 硬件的机密性和完整性:分裂制造

通过3D和2.5D集成来推进分裂制造似乎既简单又有前景。这是因为3D和2.5D集成允许将设计分成多个芯片,这些芯片可以独立维护它们的FEOL和BEOL层,而整个2.5D/3D堆栈可以包含系统级互连的进一步部分。此外,尽管进行了验证研究,但对经典分裂制造的实用性的担忧仍很普遍,因为单个芯片不必被分裂制造,而只需要整个系统。

2008年,Tezzaron Semiconductor公司概述了这种“3D拆分制造”的概念。各种各样的研究也在暗示3D拆分制造,但大多数都有一些局限性。例如,研究[23]仅停留在概念层面,而研究[24]利用2.5D集成,“仅”连接被不可信的设施隐藏。后者基本上等同于传统的分体式制造,但似乎更实用;尽管如此,研究[24]报告了相当大的布局成本。后来,促进了“原生3D拆分制造”,即在受信任和不受信任的设施之间进行逻辑拆分。

这些后来的研究的一个重要发现是,3D划分和垂直互连结构都发挥着重要作用,并定义了如下的成本——安全权衡:设计被分割到多个芯片上的越多,布局成本就越高,因为需要更多的垂直互连链路和相关电路,但却更灵活和更容易跨3D堆栈“分解”IP。

注意提出了与伪装相结合的3D分割制造。虽然研究[25]应用了常规的中心伪装,但研究[26]认为另一种伪装方法更适合3D分裂制造,即混淆垂直互连。

其他研究也建议在系统层面进行伪装。例如,[27]提出通过在“夹在”常规芯片之间的专用片上网络(NoC)芯片内重路由,来模糊3D IC的垂直互连结构。这个想法在概念上类似于[26]中的随机路由的概念,但更灵活,但也更昂贵。

3.4 硬件的机密性和完整性:木马防御

在[26]中,作者利用3D拆分制造提供的好处,推进正式安全但高成本的方案,以减少制造时的木马插入。

此外,在设计和制造期间,3D和2.5D IC似乎比2D IC更容易受到木马插入的攻击。例如,[27]中的研究认为负偏置温度不稳定性(NBTI)效应是隐蔽的特洛伊触发器,其动机是热管理是3D IC的一个众所周知的挑战。在更普遍的情况下,3D和2.5D集成相关的供应商和参与者的更广泛的前景可能为攻击者嵌入木马提供新的机会。随着晶圆级芯片级封装(WLCSP)被广泛采用,也面临着这样的安全风险。这里假设的攻击是,一些恶意的集成工具可以在目标芯片和包微碰撞之间放置一个薄的木马芯片,而该木马芯片将包含tsv,可以通过和进入这些外部连接,随意访问所有这些信号。为了避免视觉或x射线检查的发现,有人认为将这些tsv与微凸点位置对齐可能就足够了。

然而,在运行时木马检测可以从3D和2.5D集成中受益。这是因为相关的安全特性可以使用可信的制造过程单独实现,并在稍后与待监控的商品芯片集成/堆叠。

3.5 硬件的保密性和完整性:puf

将多个芯片集成到3D/2.5D堆栈中似乎有利于理解puf的概念,因为每个芯片都是独立的过程变化。因此,可以使用多个独立的熵源来构建puf。在[28,29]中,提出了两个这样的方案,进一步利用tsv的过程变化。虽然这些研究在原则上有希望,但没有考虑到最先进的机器学习攻击,他们的实际韧性仍有待证明。

3.6 运行时的数据安全:未经授权的访问或修改数据

3D和2.5D集成可以实现组件的物理分离,因此可以实现可靠的安全功能,如运行时监视器或验证器。

这些方案的实际实施本身可能成为一个漏洞。例如,内省接口,这需要在被监控的商品芯片中添加额外的逻辑。很容易看出,一旦这些接口被该商品芯片设计或制造的恶意行为者修改,就会失败。因此,产生了不受欢迎的依赖关系,可能会完全阻碍该计划。

例如2.5D信任根,它将不受信任的商品芯片与芯片集成到一个包含安全特性的活动中间体上,并进一步形成芯片与芯片之间系统级通信的主干。因此,商品组件和安全组件之间存在明确的物理分离,避免了任何破坏安全的依赖关系。

3.7 运行时数据安全:侧通道和故障注入攻击

总的来说,对于3D和2.5D IC来说,考虑到有源器件的密度更高,电路结构和体系结构更复杂,会导致更嘈杂的侧信道攻击变得更加困难。例如,[30]的作者研究了对3D IC的功率侧信道攻击,他们观察到来自3D IC内不同芯片的功率噪声分布是叠加的。他们还提出了一种用于加密模块的电压电源的随机交联方案,以使对此类模块的攻击更加困难。

一些现有技术也研究了明确针对3D集成电路的侧信道攻击。例如,[32]和[31]证明对3D IC的热侧信道攻击可以分别在运行时和设计时减轻。然而,[32]中的方法似乎不太实际;为了减少通过热模式的信息泄漏,它利用了额外虚拟活动的动态生成,这进一步加剧了3D集成电路的热管理挑战。相比之下,[31]的作者模拟了tsv和模块放置对楼层规划期间热分布和热泄漏的影响,从而在降低峰值温度的同时减少泄漏。

此外,一些研究利用3D和2.5D集成来倡导安全方案,被认为太昂贵。例如,文献[33]中的研究利用随机驱逐和异构延迟作为缓存架构。作者证明,这种技术在2D IC中会产生很高的性能开销,但即使在3D IC中也可以实现。

与侧信道攻击一样,由于3D/2.5D IC的物理封装,故障注入攻击可能会变得更加困难。

尽管如此,在[34]中,最近的研究表明,横向重新排列激光装置足以使这种故障注入攻击成为可能,同样适用于背面保护的2D IC,也可能适用于2.5D和3D IC。然而,如果3D集成电路采用专用的物理设计,例如将tsv密集地放置在芯片边界处,形成“垂直屏蔽”结构,同时在BEOL中使用常规的屏蔽和背面保护。

3.8 运行时的数据安全:物理读出和探测攻击

类似于故障注入攻击,3D/2.5D集成启用的物理框的概念可能会阻碍读取和探测攻击。在[35]中,作者主张3D IC支持“全方位屏蔽”。类似的防止探测的保护在之前已经讨论过。

参考文献

[1] J. Rajendran et al., “Nano meets security: Exploring nanoelectronic devices for security applications,” Proc. IEEE, vol. 103, no. 5, pp. 829–849, 2015. https: //doi.org/10.1109/JPROC.2014.2387353

[2] S. Ghosh, “Spintronics and security: Prospects, vulnerabilities, attack models, and preventions,” Proc. IEEE, vol. 104, no. 10, pp. 1864–1893, 2016. https://doi. org/10.1109/JPROC.2016.2583419

[3] F. Rahman et al., “Security beyond CMOS: Fundamentals, applications, and roadmap,” Trans. VLSI Syst., vol. PP, no. 99, pp. 1–14, 2017. https://doi.org/10. 1109/TVLSI.2017.2742943

[4] Q. Alasad, J. Yuan, and D. Fan, “Leveraging all-spin logic to improve hardware security,” in Proc. Great Lakes Symp. VLSI, 2017, pp. 491–494. https://doi.org/10. 1145/3060403.3060471

[5] T. Winograd et al., “Hybrid STT-CMOS designs for reverse-engineering prevention,” in Proc. Des. Autom. Conf., 2016, pp. 88–93. https://doi.org/10.1145/ 2897937.2898099

[6] S. Patnaik et al., “Spin-orbit torque devices for hardware security: From deterministic to probabilistic regime,” Trans. Comp.-Aided Des. Integ. Circ. Sys., vol. 39, pp. 1591–1606, 2019. https://doi.org/10.1109/TCAD.2019.2917856

[7] F. Parveen, Z. He, S. Angizi, and D. Fan, “Hybrid polymorphic logic gate with 5-terminal magnetic domain wall motion device,” in Proc. Comp. Soc. Symp. VLSI, 2017, pp. 152–157. https://doi.org/10.1109/ISVLSI.2017.35

[8] S. Patnaik et al., “Advancing hardware security using polymorphic and stochastic spin-hall effect devices,” in Proc. Des. Autom. Test Europe, 2018, pp. 97–102. https://doi.org/10.23919/DATE.2018.8341986

[9] N. Rangarajan et al., “Opening the doors to dynamic camouflaging: Harnessing the power of polymorphic devices,” Trans. Emerg. Top. Comp., vol. Early Access, 2020. https://doi.org/10.1109/TETC.2020.2991134

[10] A. Roohi and R. F. DeMara, “PARC: A novel design methodology for power analysis resilient circuits using spintronics,” Trans. Nanotech., vol. 18, pp. 885– 889, 2019. https://doi.org/10.1109/TNANO.2019.2934887

[11] A. S. Iyengar, S. Ghosh, and K. Ramclam, “Domain wall magnets for embedded memory and hardware security,” J. Emerg. Sel. Topics Circ. Sys., vol. 5, no. 1, pp. 40–50, 2015. https://doi.org/10.1109/JETCAS.2015.2398232

[12] N. Rangarajan, A. Parthasarathy, and S. Rakheja, “A spin-based true random number generator exploiting the stochastic precessional switching of nanomagnets,” J. Appl. Phys., vol. 121, no. 22, p. 223905, 2017. https://doi.org/10.1063/1.4985702

[13] N. Rangarajan et al., “SMART: A secure magnetoelectric antiferromagnet-based tamper-proof non-volatile memory,” vol. 8, pp. 76 130–76 142, 2020. https://doi. org/10.1109/ACCESS.2020.2988889

[14] H. Nili et al., “Hardware-intrinsic security primitives enabled by analogue state and nonlinear conductance variations in integrated memristors,” Nature Electronics, vol. 1, no. 3, pp. 197–202, 2018. https://doi.org/10.1038/s41928-018-0039-7

[15] A. Rezaei, J. Gu, and H. Zhou, “Hybrid memristor-CMOS obfuscation against untrusted foundries,” in Proc. Comp. Soc. Symp. VLSI, 2019, pp. 535–540. https: //doi.org/10.1109/ISVLSI.2019.00102

[16] L. Liu, H. Huang, and S. Hu, “Lorenz chaotic system-based carbon nanotube physical unclonable functions,” Trans. Comp.-Aided Des. Integ. Circ. Sys., vol. 37, no. 7, pp. 1408–1421, 2018. https://doi.org/10.1109/TCAD.2017.2762919

[17] C. K. H. Suresh, B. Mazumdar, S. S. Ali, and O. Sinanoglu, “A comparative security analysis of current and emerging technologies,” Micro, vol. 36, no. 5, pp. 50–61, 2016. https://doi.org/10.1109/MM.2016.87

[18] Y. Bi et al., “Emerging technology-based design of primitives for hardware security,” J. Emerg. Tech. Comp. Sys., vol. 13, no. 1, pp. 3:1–3:19, 2016. https: //doi.org/10.1145/2816818

[19] S. Rai et al., “Security promises and vulnerabilities in emerging reconfigurable nanotechnology-based circuits,” Trans. Emerg. Top. Comp., vol. Early Access, 2020. https://doi.org/10.1109/TETC.2020.3039375

[20] Y. Cui et al., “Encoding molecular information in plasmonic nanostructures for anti-counterfeiting applications,” Nanoscale, no. 6, pp. 282–288, 2014. https: //doi.org/10.1039/C3NR04375D

[21] J. Knechtel, S. Patnaik, and O. Sinanoglu, “3D integration: Another dimension toward hardware security,” in Proc. Int. On-Line Test Symp., 2019, pp. 147–150. https://doi.org/10.1109/IOLTS.2019.8854395

[22] C. Yan et al., “Hardware-efficient logic camouflaging for monolithic 3D ICs,” Trans. Circ. Sys., vol. 65, no. 6, pp. 799–803, 2018. https://doi.org/10.1109/TCSII. 2017.2749523

[23] J. Dofe et al., “Security threats and countermeasures in three-dimensional integrated circuits,” in Proc. Great Lakes Symp. VLSI, 2017, pp. 321–326. https: //doi.org/10.1145/3060403.3060500

[24] Y. Xie, C. Bao, and A. Srivastava, “Security-aware 2.5D integrated circuit design flow against hardware IP piracy,” Computer, vol. 50, no. 5, pp. 62–71, 2017. https://doi.org/10.1109/MC.2017.121

[25] P. Gu et al., “Cost-efficient 3D integration to hinder reverse engineering during and after manufacturing,” in Proc. Asian Hardw.-Orient. Sec. Trust Symp., 2018, pp. 74–79. https://doi.org/10.1109/AsianHOST.2018.8607176

[26] S. Patnaik, M. Ashraf, O. Sinanoglu, and J. Knechtel, “A modern approach to IP protection and trojan prevention: Split manufacturing for 3D ICs and obfuscation of vertical interconnects,” Trans. Emerg. Top. Comp., vol. Early Access, 2019. https://doi.org/10.1109/TETC.2019.2933572

[27] J. Dofe, Q. Yu, H. Wang, and E. Salman, “Hardware security threats and potential countermeasures in emerging 3D ICs,” in Proc. Great Lakes Symp. VLSI, 2016, pp. 69–74. https://doi.org/10.1145/2902961.2903014

[28] M. Wang, A. Yates, and I. L. Markov, “SuperPUF: Integrating heterogeneous physically unclonable functions,” in Proc. Int. Conf. Comp.-Aided Des., 2014, pp. 454–461. https://doi.org/10.1109/ICCAD.2014.7001391

[29] C. Wang et al., “TSV-based PUF circuit for 3DIC sensor nodes in IoT applications,” in Proc. Electron. Dev. Solid State Circ., 2015, pp. 313–316. https://doi.org/10.1109/ EDSSC.2015.7285113

[30] J. Dofe and Q. Yu, “Exploiting PDN noise to thwart correlation power analysis attacks in 3D ICs,” in Proc. Int. Worksh. Sys.-Level Interconn. Pred., 2018. https: //doi.org/10.1145/3225209.3225212

[31] J. Knechtel and O. Sinanoglu, “On mitigation of side-channel attacks in 3D ICs: Decorrelating thermal patterns from power and activity,” in Proc. Des. Autom. Conf., 2017, pp. 12:1–12:6. https://doi.org/10.1145/3061639.3062293

[32] P. Gu et al., “Thermal-aware 3D design for side-channel information leakage,” in Proc. Int. Conf. Comp. Des., 2016, pp. 520–527. https://doi.org/10.1109/ICCD. 2016.7753336

[33] C. Bao and A. Srivastava, “3D integration: New opportunities in defense against cache-timing side-channel attacks,” in Proc. Int. Conf. Comp. Des., 2015, pp. 273–280. https://doi.org/10.1109/ICCD.2015.7357114

[34] J. Rodriguez, A. Baldomero, V. Montilla, and J. Mujal, “LLFI: Lateral laser fault injection attack,” in Proc. Worksh. Fault Diag. Tol. Cryptogr., 2019, pp. 41–47. https://doi.org/10.1109/FDTC.2019.00014

[35] J. Knechtel, S. Patnaik, and O. Sinanoglu, “3D integration: Another dimension toward hardware security,” in Proc. Int. On-Line Test Symp., 2019, pp. 147–150. https://doi.org/10.1109/IOLTS.2019.8854395