1 引言

之前大多数软件都是与它们各自的硬件一起发布,没有办法对其进行更改。但随着技术的成熟,制造商找到了在现有硬件上更新软件以增加附加功能的方法。

现在,想象一下未来硬件更新也成为可能——不是很有趣吗?

那么,这种可编程硬件,其子系统配置甚至在制造后也可以修改,属于可重构系统的范畴。而支持可重构计算的最主要的集成电路是FPGA,即可编程门阵列的缩写。

FPGA使您可以编程产品功能,适应新标准,并在产品安装在现场后针对特定应用重新配置硬件——因此称为“现场可编程”。而“门阵列”指的是其架构中存在的二维逻辑门阵列。

所有现代个人计算机,包括台式机、笔记本、智能手机和平板电脑,都是通用计算机的例子。通用计算采用“冯·诺依曼”方法,即指令获取和数据操作不能同时发生。因此,它们是顺序机器,其性能也受到限制。

另一方面,我们有应用特定集成电路(ASIC),这些电路是为特定任务定制的,例如数字语音记录器或高效的比特币矿工。ASIC使用空间方法来实现只实现一个特定应用程序,并将电路中的元件针对该应用程序进行了高度优化,提供了最大的性能。但是由于ASIC的电路结构非常专门化,它只能用于执行被设计的特定任务,不能用于其他任务。

那么,为了获得ASIC的高性能,是否需要牺牲通用处理器的灵活性呢?

实际上FPGA处于这两种架构范式之间,具有一定的灵活性和可重构性!

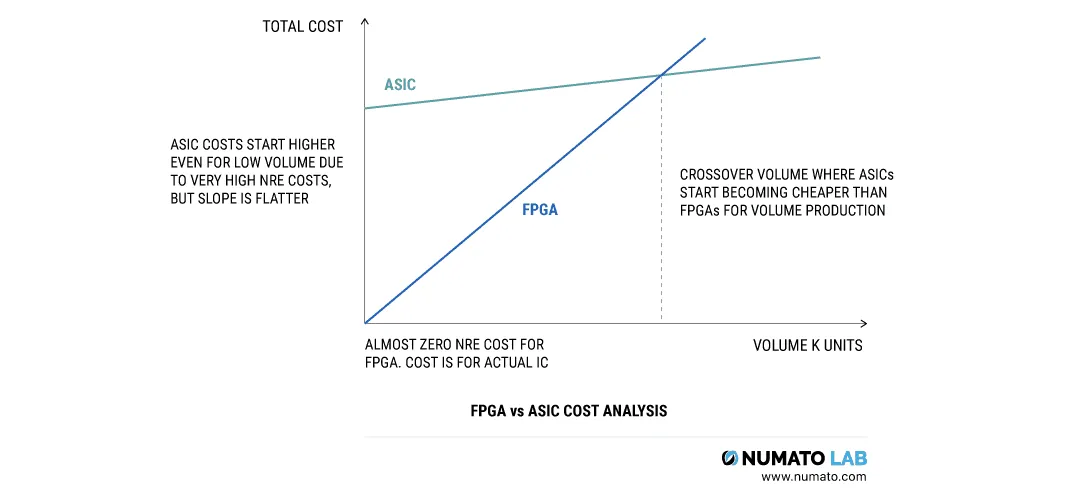

虽然FPGA具有可重新编程和相对较低的NRE(非重复性工程)成本等优势,但与ASIC相比,FPGA的能源效率较低(指在完成特定计算任务时所消耗的能量与计算任务完成的速度之比),且不适用于大规模生产。

因此,ASIC和FPGA具有不同的优势和价值主张。通常,大多数设备制造商会使用FPGA进行原型设计,因为它们可以快速迭代和测试不同的设计,且具有一定的灵活性。而在确定了最终的设计之后,制造商通常会使用ASIC进行大规模生产,以获得更高的性能和更低的成本。

过去,FPGA通常被用于较低速度和复杂设计,因为FPGA的电路结构相对复杂处理速度相对较低;且其可编程性和灵活性使FPGA更适用于那些需要实现较为复杂设计的场合。但是现在随着FPGA技术的不断发展和改进,FPGA已经能够实现更高的处理速度和更优化的电路结构。目前,FPGA已经可以轻松地实现超过500MHz的处理性能基准。

2 FPGA的内部架构

1985年,一家名为Xilinx的半导体制造公司发明了第一个商业化的FPGA芯片XC2064。另一家在2015年被英特尔收购的公司Altera也推动了市场的发展,并与Xilinx一起推动了FPGA技术的发展。

FPGA起源于相对较简单的技术,如可编程只读存储器(PROM)和可编程逻辑器件(PLD),如PAL、PLA或复杂PLD(CPLD)。

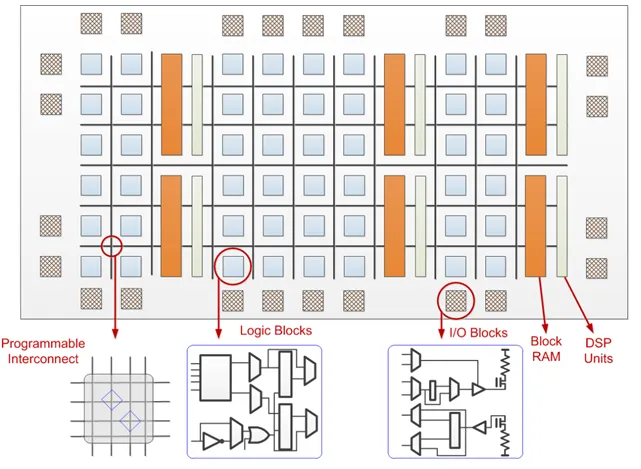

FPGA由三个主要部分组成:

- 可配置逻辑块 - 实现逻辑功能。

- 可编程互联 - 实现路由功能。

- 可编程输入/输出块 - 与外部元件连接。

逻辑块实现设计所需的逻辑功能,由各种组件组成,例如晶体管对、查找表(LUT)、触发器和多路复用器。

您可以将逻辑块视为单独的模块,就像乐高积木一样,并且可以并行操作。但与乐高积木不同的是,逻辑块是可配置的,即其内部状态可以进行控制,并且可以通过编程互联将它们连接在一起以构建有意义的东西。

可编程互联的层次结构用于在可配置逻辑块(CLB)之间分配资源;其中路由路径包含可通过反熔丝或基于存储器的技术连接的具有不同长度的电线段。

每个CLB都与交换矩阵相结合,以访问通用路由结构。交换矩阵提供可编程的多路复用器,用于选择给定路由通道中的信号,并因此连接垂直和水平线。

最后,输入/输出块(IOB)用于将CLB和路由架构与外部元件接口。

在早期的FPGA芯片中,没有处理器来运行任何软件,实现应用程序意味着从头设计电路。因此,我们可以将FPGA配置得像OR门一样简单,也可以像多核处理器一样复杂。

但是自XC2064以来,FPGA的基本架构已经通过添加更多专门的可编程功能块(如ALU、块RAM、多路复用器、DSP-48和微处理器)而得到发展。

3 FPGA设计流程

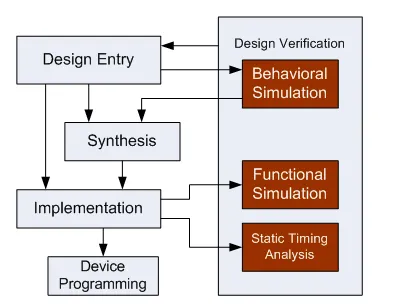

设计流程描述了在物理板上实现和编程任何给定逻辑的流程。于该流程与软件开发生命周期(SDLC)类比,我将其称为 FPGA 开发生命周期(FDLC)。

FPGA架构设计流程包括设计输入、逻辑综合、设计实现、设备编程和设计验证等步骤。然而,具体步骤因制造商而异。

4 设计输入

逻辑的描述可以使用原理图编辑器、有限状态机(FSM)编辑器或硬件描述语言(HDL)来制作。这是通过从给定库中选择组件并将设计函数直接映射到所选的计算块来完成的。

当设计具有大量功能时,图形化管理变得困难,此时可以使用HDL以结构化或行为方式捕捉设计。除了已经成为最常用的HDL语言之一的VHDL和Verilog之外,还有一些类似于C语言的HDL语言可供选择,如Handel-C、Impulse C和SystemC等。

使用HDL进行设计描述,可以更直观地表达设计的结构和行为,并方便设计的复用和修改。同时,HDL还可以进行仿真验证,确保设计的正确性和可靠性。因此,HDL在FPGA设计中具有广泛的应用价值。

5 逻辑综合

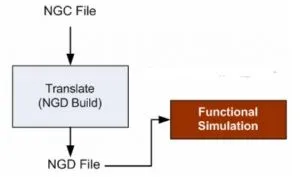

这个过程将上述VHDL代码翻译成设备网表格式,以描述具有逻辑元素的完整电路。综合过程涉及检查代码语法和分析设计体系结构的层次结构。接下来是将代码与优化一起编译,并将生成的网表保存为.ngc文件。

6 设计实现

设计实现过程包括以下步骤:

- 翻译:合并所有输入网表到逻辑设计文件中,生成 .ngd 文件。用户约束文件为端口指定物理元素。

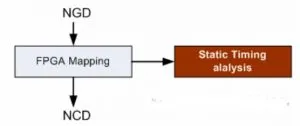

- 映射:将.ngd文件中定义的逻辑映射到FPGA器件的组件上,并生成 .ncd 文件。

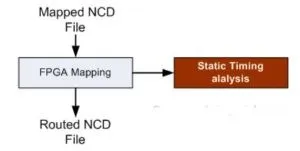

- 布局布线:按照约束条件,将上述过程中的子块放置到逻辑块中,然后连接这些块。

7 设备编程

将上述路由好的设计加载并转换为FPGA支持的格式。将路由好的.ncd文件传递给BitGen程序,生成一个包含所有FPGA编程信息的比特流文件。

8 设计验证

这个过程是与设计流程一起完成的,以确保逻辑行为符合预期。这个过程涉及以下仿真:

- 行为仿真(RTL仿真)

- 功能仿真

- 静态时序仿真

通过为设计提供各种输入测试模式,并观察输出,这些仿真可以模拟设计的行为,从而验证其正确性和可靠性。设计验证过程是确保设计质量的关键步骤,可以在设计实现之前或之后进行。

9 FPGA的未来

产业趋势将FPGA推向在异构计算范例中越来越重要的作用。这里的异构计算是指使用多种类型的处理器来执行各自的专门处理能力的系统。而所有这些不同的处理器,包括FPGA,都可以通过OpenCL进行编程——这是一个行业标准的开发平台。

FPGA提供了成本效益的并行计算能力,适用于快速原型制作。在测试神经网络时,FPGA有时也能够超越GPU。虽然GPU对于训练来说可能很好,但当涉及实时应用时,FPGA更加适应。微软已经在通过Microsoft Azure云服务加速AI时使用了英特尔Stratix FPGA。