了解英伟达的研发情况,已经成为每年英伟达春季GTC会议的一个常规特征。

比如首席科学家兼研究部高级副总裁Bill Dally每年就会提供英伟达研发机构的概况和关于当前优先事项的一些细节。

2022年,Dally主要关注英伟达正在开发和使用的AI工具,这些AI正在改善英伟达自身的产品。

如果愿意接受的话,这其实是一个巧妙的反向营销案例:英伟达从制作显卡来做跑AI工具的公司,成为了一家AI工具用来做显卡的公司。

是的,英伟达已经开始使用AI智能来有效改善和加快自家的显卡设计。

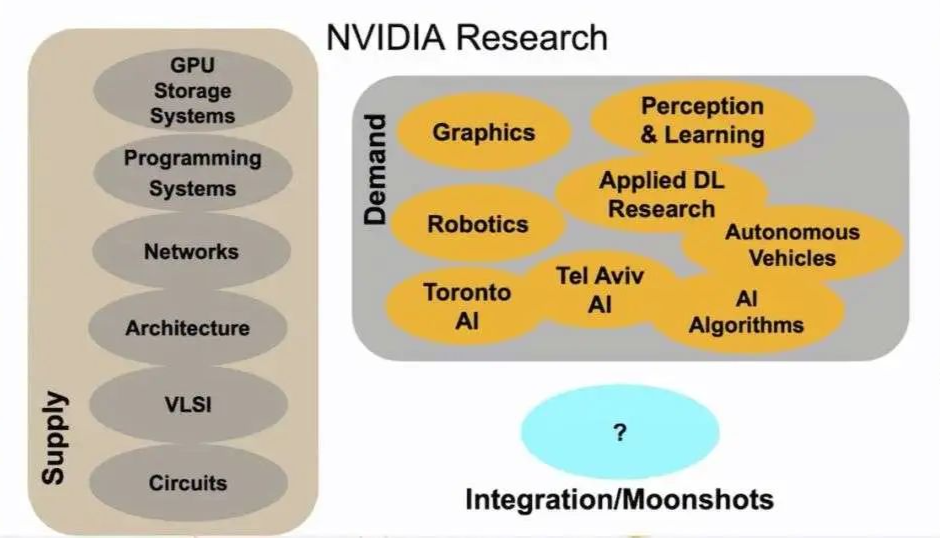

Dally在2022年的GTC演讲中描述道:「我们的设计团队是一个约有300人的小组,试图在英伟达的产品设计上探索更有前瞻性的领先位置。我们有点像远光灯,试图照亮远处的东西。这个团队被松散地组织成两半。

供应部分负责提供显卡的技术。它使显卡本身更好,从电路、到超大规模集成设计方法、架构网络、编程系统,以及读入显卡和基于显卡的软件的存储系统。」

「需求部分试图通过开发要用显卡才能良好运行的软件系统和技术,来推动市场对英伟达产品的需求。

例如我们有三个不同的图形研究小组,因为我们在不断推动计算机图形技术的发展。我们还有五个不同的人工智能小组,因为使用GPU来运行AI是目前一个巨大的热门,而且只会越来越热。我们也有做机器人和自动驾驶汽车的小组。」

「我们还有一些以地域为导向的实验室,如我们的多伦多和特拉维夫人工智能实验室。」

偶尔,英伟达公司会从这几个小组中抽出部分人力重组个登月式项目,例如,其中一次此类项目产生了英伟达的实时光线追踪技术。

光追项目的组织架构图

一如既往,2022年的研究与Dally上一年的谈话有重复之处,但也有新的信息。比如该部门的规模肯定已经从2019年的175人左右增长了很多。毫无疑问,英伟达开发自动驾驶系统和机器人的努力也已经加强了。Dally没有多说CPU的设计工作,这无疑也在增强。

接下来呈现的是Dally演讲中关于英伟达在设计芯片时越来越多地使用AI的一小部分内容。

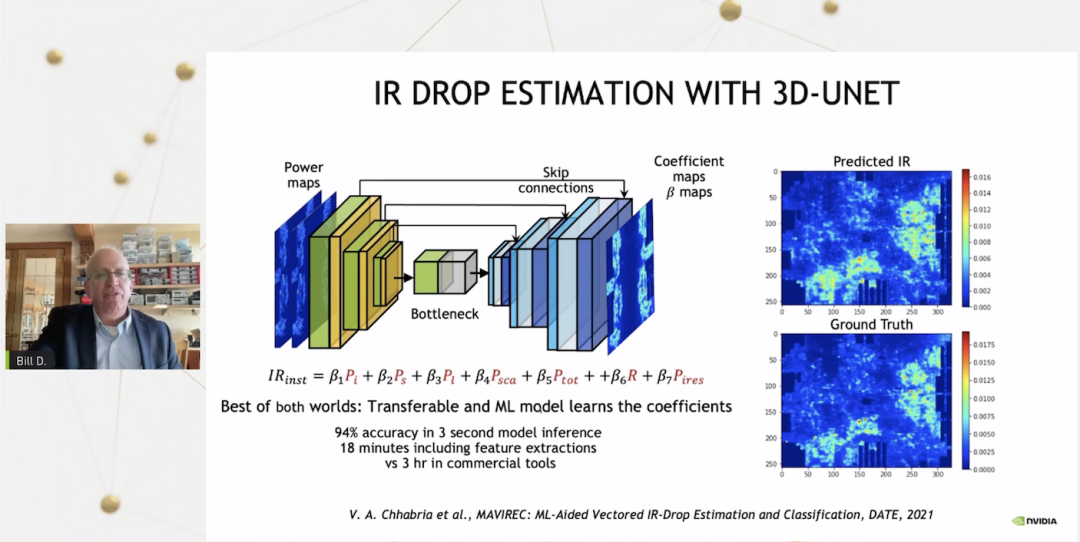

绘制电压下降图

Dally指出:「作为人工智能的专家,我们自然希望利用AI来设计更好的芯片。」

英伟达的显卡设计部门以几种不同的方式做到这一点。第一个也是最明显的方法是,可以利用现有的计算机辅助设计工具,并将AI模型纳入其中。

例如,显卡设计部门有一个辅助设计的软件工具,其中的AI实时测绘了英伟达的GPU显卡产品中使用电力变化的位置图谱,并实时预测电压网格下降的程度。

一般电压下降是用电流乘以电阻下降度算出,要在传统的CAD工具上运算出这个值需要三个小时。因为这是一个迭代的过程,一直用传统工具的话,对设计部门来说,工作量会变得非常艰巨。

概念展示

英伟达的显卡设计部门想做的是训练一个AI模型来获取相同的数据。开发人员在一堆设计上如此试行过后,然后给AI输入功率图。AI由此产生的推理时间只有三秒。

当然,如果你包括上功率图特征值提取的时间,那就是18分钟。无论如何,与传统效果相比这都是非常快的结果。

在类似的前提情况下,显卡设计部门还尝试了不使用卷积神经网络AI、而是使用图神经网络的AI。如此处理的目的是为了估计显卡电路中不同节点的开关频率,这实际上推动了前述例子中的功率特征值输入效率。

附带的效果是,英伟达的开发人员能够得到非常准确的显卡电路功率估计,比传统工具要快得多,而且只用了很小的一部分时间。

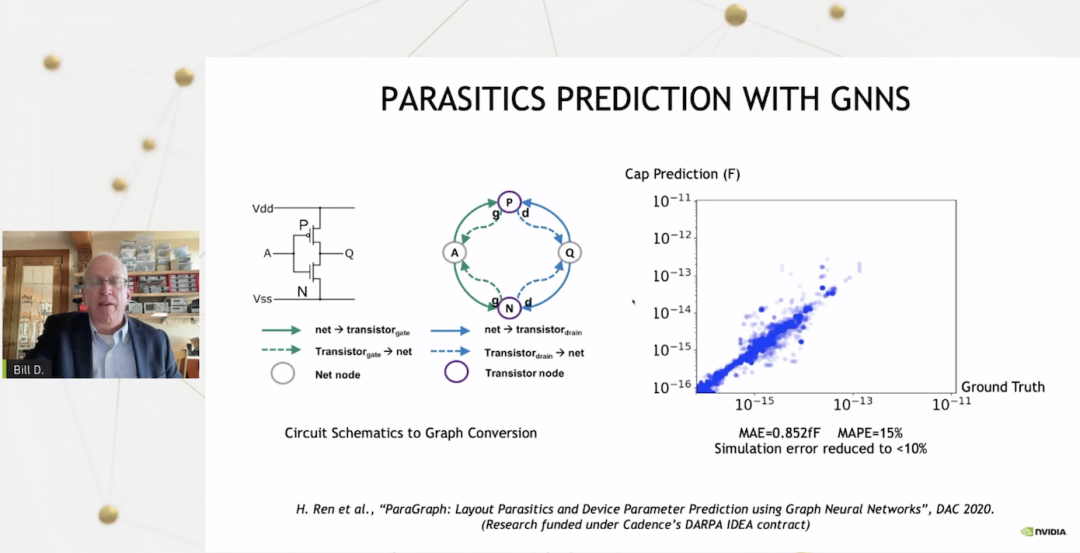

预测寄生元件

Dally特别喜欢的、若干年前他作为一名电路设计师投入相当多时间的设计项目,是用图形神经网络AI预测寄生元件(设计时未曾打算或预料到的电子元件)将会如何被附加到最终成品中。

过去,电路设计是一个非常反复的过程,设计师会画出一个带了一堆晶体管标志的电路原理图。但他不会知道电路板的性能如何。

直到布局设计师拿着这个原理图,做了布局样品,附加了寄生元件,然后设计者才可以运行电路模拟,发现其中哪些部分不符合预期的设计规格。

然后设计师会返回去修改他的原理图,并再次麻烦布局设计师再跑一遍这个流程,这是一个非常漫长的、反复的、不人性的劳动密集型过程。

现在英伟达的显卡设计部门可以做到的,是训练神经网络来预测寄生元件,而不需要让布局设计师制造布局样品才发现瑕疵。

因此,电路设计者可以非常快速地迭代,而不需要在循环中重复进行手动设计-布局-再设计的步骤。

按Dally表示,与基础真实值相比,现在英伟达的设计AI对这些寄生器件的预测非常准确。

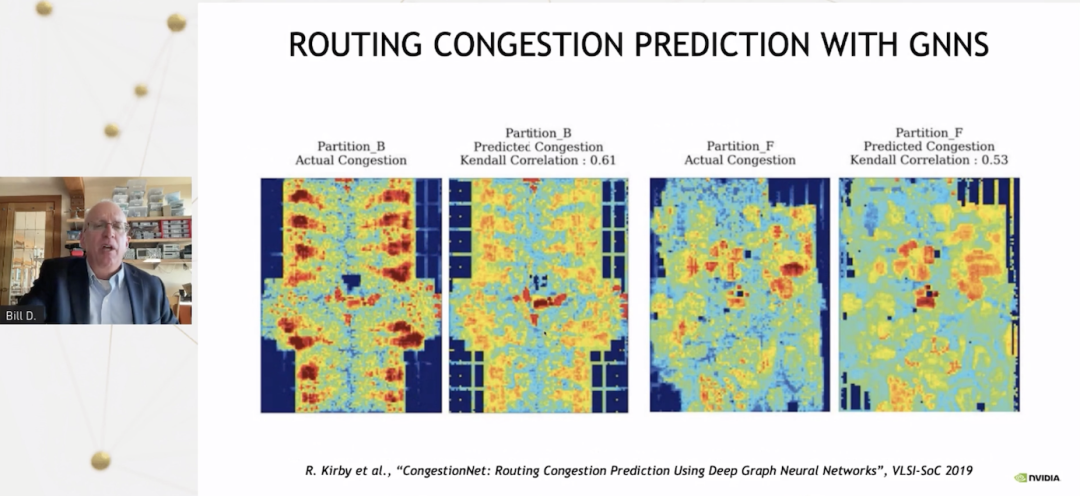

布局/布线拥塞

同时,我们还可以预测芯片的布局/布线带来的拥塞问题,这对芯片的布局至关重要。

按正常的流程,芯片设计人员会做一张网格表,运行一遍布局和布线的过程。一般这个过程非常耗时,会花费数天的时间。

只有如此设计师们才能获得显卡样品实际的拥塞情况,光有设计图的初始布局是不够的。

设计师们需要将其重构,并以不同的方式放置宏,以避开红色的区域(如下图所示)。红色区域有太多交错的线路穿过给定的区域,就像比特版「交通堵塞」。

而像这种情况,用上辅助设计的AI之后,没必要再跑一边布局和布线,就可以拿着这些网格列表,并用图像神经网络AI对拥塞出现的位置进行基本预测,结果还算准确。

虽说还不算完美,但是能显示哪些区域存在问题。之后设计团队就可以在特定区域采取行动,快速完成迭代,不再需要一遍遍重复全局布局和布线了。

芯片标准单元设计自动化

现有的方法都是用AI来评价人类的设计,而未来,更令人兴奋的是能够使用AI来完成设计。

Dally举了两个例子来说明AI如何完成芯片设计。

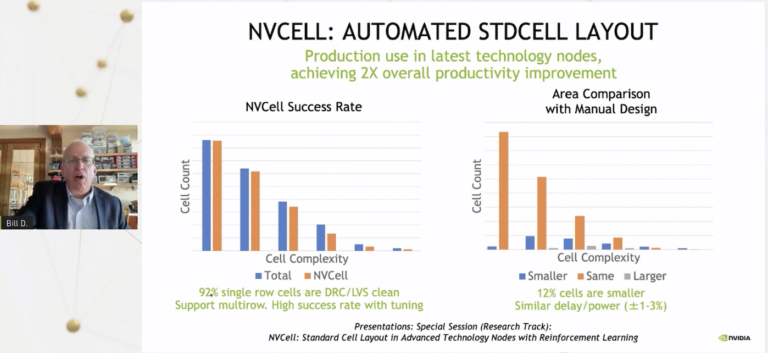

第一个系统叫NVCell,它结合了模拟低温退火和加强学习,基本上能够设计出数字集成电路的标准单元库。

每次设计师实现了芯片技术上的升级——比方说从7纳米优化到5纳米,设计师都会创造出一个单元库。

一个单元就像是一个「与门」和「或门」,是一种完全的加速器。

眼下,英伟达的设计部门有数千个这种单元库。这些单元需要在新技术的框架下,遵循一套复杂的设计标准,被重新设计。

第二个,是用强化学习模型来设计晶体管布局。

设计师们大部分都采用强化学习的办法来放置晶体管。然而更重要的是,在晶体管放置后,一般都有很多设计规则上的错误,找到这些错误就像一款电子游戏一样。

事实上,强化学习就擅长这个。一个很好的例子就是,强化学习在Atari电子游戏上的应用。

所以,这就像是一款Atari电子游戏,只不过,这次是一款修正标准单元中设计上存在的错误的游戏。

通过强化学习,英伟达的设计师可以筛查一遍出现的设计规则错误,然后修正它们。这样,设计师就可以基本完成标准单元的设计工作了。

如下图所示,92%的单元库都可以用这个工具做好,不会存在任何设计规则上的错误或是电路上的错误。

此外,12%的单元比人工设计的单元都要小。总的来说,从单元的复杂性上看,AI设计的单元和人工设计的一样好。

这可以帮助设计师完成两件事。

第一,应用AI能极大地节省劳动力。没有AI的话,大约需要一个10人小组耗时一年来建立一个新的技术库。而如今,设计师可以用几个GPU,跑几天就行。

然后,人工只用介入剩下那8%AI未能完成的单元就好了。

在大多数情况下,设计师凭借AI往往能做出更好的设计。

所以说,不光省时省力,做出来的东西还更好。