目前雷达芯片中GaAs(砷化镓)技术已经被淘汰,SiGe(硅锗)主要用于LRR芯片组。从SiGe到CMOS的过渡始于NXP在2015年推出的用于后向雷达的Dolphin芯片组。CMOS技术将雷达功能进一步整合到单个芯片上,实现了大规模量产并降低了成本。

向CMOS技术的转变使得混合信号和射频功能被整合到单个AFE(模拟前端)芯片上,并将功率放大器功能进一步整合到MMIC(单片微波集成电路)上。

更先进的节点

雷达芯片组的下一个趋势是向更小的工艺节点发展,以提高集成度,从而降低尺寸和功耗。

Infineon的MMIC发展到了28nm CMOS。Bosch正在利用Global Foundries的22FDX工艺技术,采用22nm FD-SOI(Fully-Depleted Silicon-on-Insulator)。NXP的雷达芯片组平台正在转向16nm TSMC FinFET,以支持其成像雷达产品,并制定了向更小节点发展的路线图。

芯片平台策略

另一个趋势是,汽车半导体供应商正在开发一个芯片组平台,可以覆盖所有类型的汽车雷达,从角雷达SRR到4D成像雷达LRR,通过“级联”几个芯片来提供成像雷达所需的高性能,同时利用规模效益来降低单位成本。

比如,Infineon的RASIC MMIC与AURIX TriCore MCU,和NXP的TEF82xx MMIC与S32R MCU。

通过级联,供应商可以利用低成本、低分辨率2D雷达的技术,来支持高性能4D成像雷达的新兴需求,但无需为后者开发和生产定制与分立产品。例如,NXP提供额外的TEF82xx收发器,并将MCU换成S32R45用于成像雷达。

但也有一些成像雷达开发商声称,级联策略不能提供足够的虚拟通道,所以不能提供足够的分辨率。使用”级联“解决方案的多个芯片和尺寸也会导致功耗和尺寸的更大问题。

处理器

雷达处理器通常使用32位MCU。但未来汽车雷达的性能会不断提高,需要额外的处理能力,从密集的点云分析到使用AI算法来识别FoV中的目标物体等。处理性能、复杂性、尺寸和功耗等诸多挑战的出现,有人提出使用多个处理器或ASIC的多通道成像雷达的概念。随着IVN的限制,边缘处理将在未来的雷达中至关重要。

现有汽车雷达中的典型MCU主要包括有以下几种。Infineon Aurix TC3A三核MCU,频率300MHz;NXP S32R294双核MCU(有双锁步内核),频率500MHz;Renesas RH850/V1R-M双核MCU,频率320MHz(3.2 DMIPS/MHz);Calterah Alps SoC有一个ARC EM6 CPU,频率300MHz。

用于汽车雷达的典型加速器包括,Infineon SPU 2.0(与Aurix TC3A MCU一起使用);TI AWR1234 SoC中的DSP,能够在成像雷达中生成点云,进行物体分类;Xilinx FPGA和相关的MPSoC等。

Xilinx的FPGA加速器

FPGA因其并行处理架构,可以提供未来雷达所需的高性能。但Tier1仍然认为价格太高。

部分Tier1甚至打算在成像雷达中使用带加速器的多核MCU。成像雷达初创公司Zendar将在其两个参考设计传感器中使用标准SoC,而Metawave将利用现有的IC供应商来开发其Marconi PoC的AiP(Antenna in Package)雷达。

大陆将使用Xilinx UltraScale+ MPSoCs。ARS540 LRR 4D成像雷达有196个虚拟通道,处于在研成像雷达领域中的高端产品,但仍远低于高分辨率LiDAR。在成像雷达开发商中,还有两家已量产出货的Tier1也在使用Xilinx的产品。

FPGA可以提高处理性能,包括处理增加的数据量、执行复杂计算的能力,以及在云端实现软件分析和更新车载软件。

虽然成本很高,但需要处理的信号数据量将从现有2D雷达的水平大幅增加,从大约10MBPS增加到约30GBPS。以太网还不能将原始数据发送到中央处理器,因此像FPGA这样的高性能边缘计算是必要的。虽然Metawave说Nvidia等公司的GPU比FPGA性能更好,但集中计算和高功耗意味着它们不适合像雷达这样的边缘处理应用。随着未来汽车的其他应用对高性能处理的需求不断增加,如ADAS,这些应用有更多的具体要求,据说对ASSP(Application Specific Standard Products)的需求正在减少。

不仅数据水平具有挑战性,数据信号的计算在成像雷达中也是四倍以上。成像雷达中的信号处理技术并不新鲜,但开发商之间没有共性,还没有整合。

FPGA还能实现OTA更新,并能使用云分析技术来验证软件算法是否能进行物体分类。

同时,大部分LiDAR和成像雷达初创公司坚持认为,他们会开发自己的ASIC,以提高数据处理效率,降低尺寸和功耗。但对于汽车领域的新玩家来说,芯片自研是一个挑战,他们的ASIC缺少降本所需的规模。

随着越来越多的传感器概念,对基于FPGA的需求将增加,这样就可以使FPGA供应商的成本降低。

EnSilica协处理器

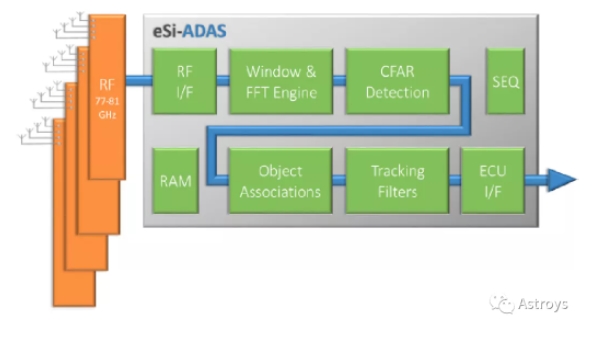

严格来说,EnSilica eSi-ADAS协处理器不是加速器,它将目标跟踪处理从雷达的ECU中释放了出来,使ECU能够专注于安全关键决策,如物体分类和传感器融合。目前eSi-ADAS已是第三代产品。

据称eSi-ADAS可以降低ADAS系统的成本,减少功耗,加快实时跟踪,最大延迟为20毫秒。

该协处理ASIC基于TSMC 180nm、24-pin QFN封装,符合AEC-Q100-2并支持ISO 26262功能安全。

它还支持基于摄像头的ADAS和其他汽车领域,包括数字仪表、电动化动力系统和信息娱乐系统。

其它要求

IVN

汽车雷达通常需要与CAN总线联网,2012年发布的CAN-FD和2018年发布的CAN-XL分别提供5/10MBPS的带宽。

未来可能会慢慢转向汽车以太网,但受到高成本、向集中式处理架构变化还没那么快,还有其他高带宽IVN协议(如MIPI CSI-2)的竞争使用的阻碍。

在未来,雷达有可能成为”哑传感器“,其处理过程被转移到中央自动驾驶处理模块,用于传感器融合。但成像雷达的高数据速率和数据压缩会给集中式架构带来挑战,特别是摄像头和激光雷达的分辨率也在提高,比如800MP的摄像头和高清环视系统等纷纷上车。

因此,至少在中短期内,传感器边缘处理仍将是一种主流的处理拓扑架构,使FPGA等供应商受益。到目前为止,车厂还没有确认他们对ADAS和AD的处理架构和传感器的计划,只有少数厂商使用集中式域控。但一旦带宽问题被克服,像Echodyne等认知型雷达概念将实现传感器的集中控制。

内存

汽车雷达通常需要2MB左右的RAM闪存。但随着性能的提高,对内存的要求也在提高。

NXP S32R294有两个e200z7 32位处理内核,有5.5MB的SRAM,比之前Qorivva MPC577xK的1.5MB有所增加。

Infineon在2019年10月推出了TC3A,有四个300MHz的TriCore处理内核,两个额外的锁步内核,SPU 2.0 DSP和6MB的嵌入式SRAM。

TI的AWR1642有一个ARM Cortex-R4F 32位200MHz的处理内核,有256kB的程序RAM和192kB的数据RAM。它还有一个600MHz的C674x DSP,32kB的L1P、32kB的L1D和256kB的L2内存以及768kB的L3雷达内存。总的来说,AWR1642中嵌入了约1.5MB的内存。