中断是计算机系统中非常重要的部分,计算机基础理论书籍往往也会花上很多篇幅讨论中断,但是因为操作系统都替开发人员处理好中断了,所以除非是系统工程师,否则一般开发人员对中断很难有一个很直观的认识,因此理解如何通过软件的方式来模拟中断更是一个挑战。

因此,在本章中,我们简单介绍硬件中断的基本原理,然后结合中断的基本原理讨论如何虚拟化中断芯片。我们从起初IBM PC为单核系统设计的PIC(8259A)机制开始,讨论到为多核系统设计的APIC,一直到绕开I/O APIC、从设备直接向LAPIC发送基于消息的MSI机制。

中断芯片可以在用户空间中模拟,也可以在内核空间模拟,但是因为中断芯片需要密集地和Guest以及内核中的KVM模块交互,显然在内核空间模拟更合理,所以KVM在内核中实现中断芯片的模拟。最后,我们讨论了为了提高效率,Intel是如何从硬件层面对虚拟化中断进行支持的,以及KVM是如何使用他们的。

虚拟中断

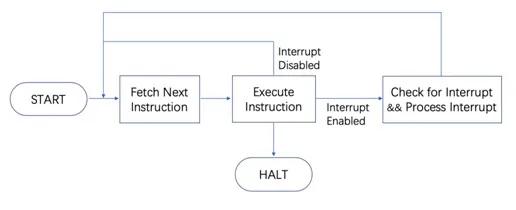

在探讨Guest模式的CPU处理中断前,我们首先回顾一下物理CPU是如何响应中断的。当操作系统允许CPU响应中断后,每当执行完一条指令后,CPU都将检查中断引脚是否有效,一旦有效,CPU将处理中断,然后再执行下一条指令,如图3-1所示。

图1 CPU处理中断

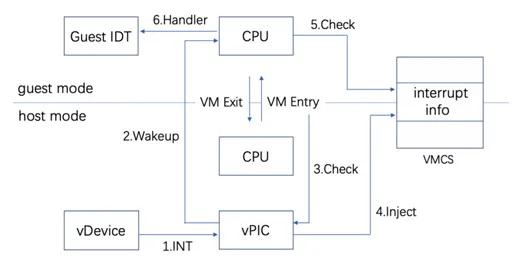

当有中断需要CPU处理时,中断芯片将有效连接CPU的INTR引脚,也就是说如果INTR是高电平有效,那么中断芯片拉高INTR引脚的电平。CPU在执行完一条指令后,将检查INTR引脚。类似的,虚拟中断也效仿这种机制,虚拟中断芯片负责将与CPU的INTR引脚相连的“引脚”有效,然后在每次VM entry时,KVM将检查虚拟中端芯片的INTR“引脚”是否有效。对于软件虚拟的中断芯片而言,“引脚”只是一个变量。如果KVM发现虚拟中断芯片有中断请求,则向VMCS中VM-entry control部分的VM-entry interruption-informationfield字段注入中断信息,然后Guest模式下的CPU将执行Guest系统IDT中对应的中断处理服务,图3-2为单核系统使用PIC中断芯片下的虚拟中断过程。

图2 基于PIC的虚拟中断过程

具体步骤如下:

1)虚拟设备向虚拟中断芯片PIC发送中断请求,虚拟PIC记录下虚拟设备的中断信息。与物理的中断过程不同,此时并不会触发虚拟PIC芯片的中断评估逻辑,而是在VM entry时进行。

2)如果虚拟CPU处于睡眠状态,则唤醒虚拟CPU,即使虚拟CPU对应的线程进入物理CPU的就绪任务队列,随时可以准备得到运行机会。

3)当虚拟CPU开始运行时,在其切入Guest前一刻,KVM模块将检查虚拟PIC芯片,查看是否有中断需要处理。此时,KVM将触发虚拟PIC芯片的中断评估逻辑。

4)一旦虚拟中断芯片计算出有需要Guest处理的中断,则将中断信息注入到VMCS中的字段VM-entry interruption-information。

5)进入Guest模式后,CPU将调用Guest IDT中相应的中断服务处理中断。

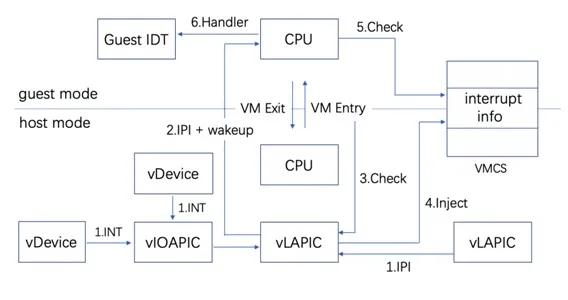

PIC只能支持单处理器系统,对于多处理器系统,需要APIC支持。对于虚拟化而言,显然也需要虚拟相应的APIC,但是其本质上与PIC基本相同,如图3-3所示。

图3 基于APIC的虚拟中断过程

与单处理器情况相比,多处理器的虚拟中断主要有2点不同:

1)在多处理器系统下,不同CPU之间需要收发中断,因此,每个CPU分别需要关联一个独立的中断芯片,这个中断芯片称为LAPIC。LAPIC不仅需要接收CPU之间核间中断IPI(Inter-Processor Interrupt),还需要接收来自外设的中断。外设的中断引脚不可能连接到每个LAPIC上,因此,有一个统一的I/O APIC芯片负责连接外设,如果一个I/O APIC引脚不够用,系统中可以使用多个I/O APIC。LAPIC和I/O APIC都接到中断总线上,通过总线进行通信。所以在虚拟化场景下,需要虚拟LAPIC和I/O APIC两个组件。

2)在多处理器情况下,仅仅是唤醒可能在睡眠的虚拟CPU线程还不够,如果虚拟CPU是在另外一颗物理CPU上运行于Guest模式,此时还需要向其发送IPI中断,使目的CPU从Guest模式退出到Host模式,然后下一次VM entry时,进行中断注入。

Guest模式的CPU和虚拟中断芯片处于两个世界,所以处于Guest模式的CPU不能检查虚拟中断芯片的引脚,只能在VM entry时由KVM模块代为检查,然后写入到VMCS。所以,一旦有中断需要注入,那么处于Guest模式的CPU一定需要VM exit,退出到Host模式,这是一个很大的开销。

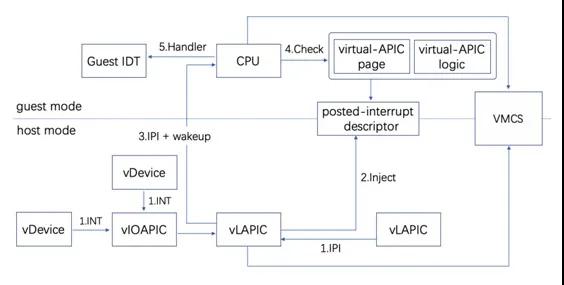

为了去除VM exit这个开销,Intel在硬件层面对中断虚拟化进行了支持。LAPIC使用一个页面大小内存存储寄存器,我们知道,当Guest访问LAPIC这些寄存器时,将导致VM exit,但是事实上,某些访问LAPIC的这些寄存器,并不需要VMM介入,所以也就无需VM exit,所以Intel实现了一个处于Guest模式的这样的一个页面,称之为virtual-APIC page。除次之外,Intel还在Guest模式下实现了部分中断芯片的逻辑,比如中断评估,我们将其称之为虚拟中断逻辑,如图4所示。

图4 硬件虚拟化支持下的中断虚拟化过程

Intel从硬件层面对虚拟化进行了支持,实现了一个处于Guest模式的用于存储中断相关寄存器的virtual-APIC page。除次之外,Intel还在Guest模式下实现了部分中断芯片的逻辑,用于中断评估和递交。

在此情况下,只要LAPIC收到中断,其不必再等待下一次VM entry时,被动执行中断评估,而是主动向处于Guest模式的CPU告知信息,这个位置就是posted-interrupt descriptor。如果目标CPU处于Guest模式,则通过一个特殊的核间中断posted-interrupt notification通知目标CPU,从而触发虚拟的中断逻辑,其会在Guest模式下进行评估评估并且向虚拟CPU递交中断,而无须再通过VM exit/VM entry的方式注入中断。

在硬件虚拟化的支持下,在Guest模式下有了状态和逻辑,就可以模拟很多中断的行为,比如访问中断寄存器、跟踪中断的状态以及向CPU递交中断等。因此,很多中断行为就无须VMM介入了,从而大大的减少了VM exit的次数。当然有些写中断寄存器的操作是具有副作用的,比如通过写icr寄存器发送IPI中断,这时就需要触发VM exit,由本地LAPIC向目标LAPIC发送IPI中断。

王柏生 资深技术专家,先后就职于中科院软件所、红旗Linux和百度,现任百度主任架构师。在操作系统、虚拟化技术、分布式系统、云计算、自动驾驶等相关领域耕耘多年,有着丰富的实践经验。著有畅销书《深度探索Linux操作系统》(2013年出版)。

谢广军 计算机专业博士,毕业于南开大学计算机系。资深技术专家,多年的IT行业工作经验。现担任百度智能云副总经理,负责云计算相关产品的研发。多年来一直从事操作系统、虚拟化技术、分布式系统、大数据、云计算等相关领域的研发工作,实践经验丰富。

本文转载自微信公众号「Linux阅码场」,可以通过以下二维码关注。转载本文请联系Linux阅码场公众号。