本文转载自微信公众号「虚机」,作者cloud3 。转载本文请联系虚机公众号。

我是cloud3,前段时间写了几篇关于高速缓存的文章,很多朋友加我好友也聊了不少。今天我们看看Cache的发展历史,这L1 L2 L3 Cache一开始是放哪里的?

好了,今天不讲原理,只看历史(intel):

无需Cache

Cache(高速缓存)的发展是计算历史上最重要的技术之一。几乎所有的现代CPU内核都设计有高速缓存。但是一开始CPU是没有Cache的,因为早期的CPU主频很低,甚至都没有内存的频率高,所以无需Cache,CPU直接读写内存。

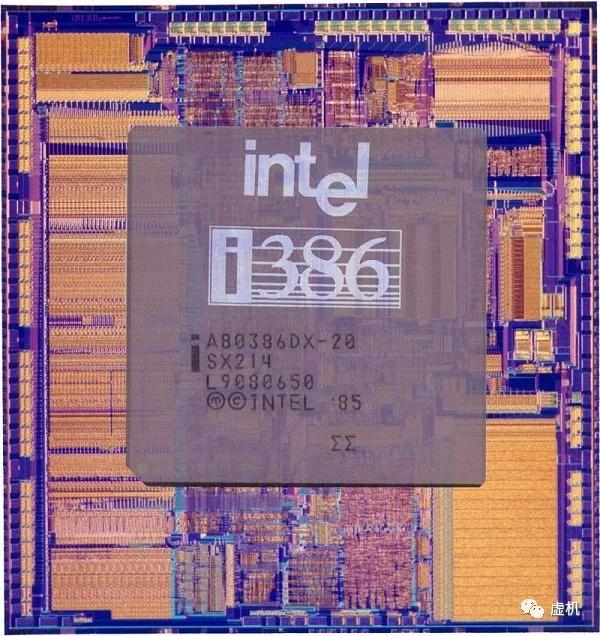

外部Cache出现

从80386开始CPU主频开始远高于内存频率。80386DX为25MHz,一个总线周期为2拍80ns,当时已没有速度相匹配的DRAM可用。在冯诺依曼结构下,CPU的访存速度就成了瓶颈,为了能够加速内存访问,Intel主板上增加了外部Cache来配合80386运行,当时的Cache都是Write-Through的。这就是最初的Cache。

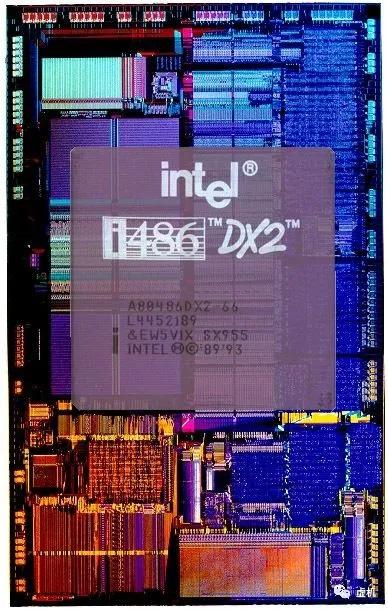

内部L1 Cache

80486开始Cache被设计在了在CPU内部,加入了8KB的L1 Cache,但是不分指令和数据Cache,同时也可以使用CPU外部主板上的Cache,即L2 Cache,大小从128KB到256KB不等。80486内部的Cache是4路组相联的设计,并且增加了Write-back的Cache属性。

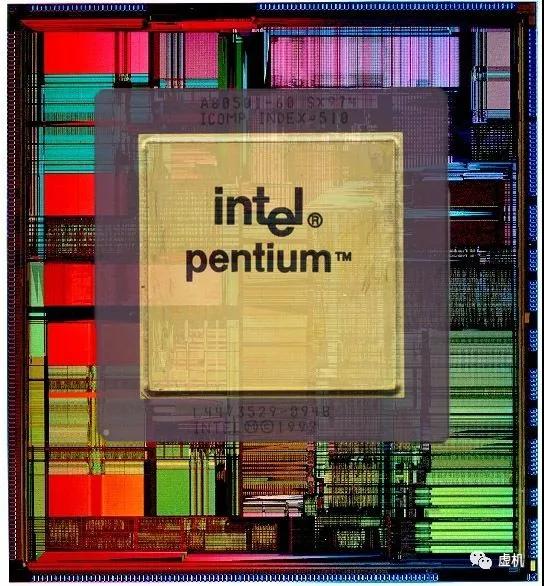

指令和数据Cache分开

到了80586/Pentium-1,Intel采用了双路执行的超标量结构,有2条并行整数流水线,需要对数据和指令进行双重访问,为了使访问互不干涉,于是L1 Cache被一分为二,分为指令Cache和数据Cache,都是8KB大小。这就是iCache和dCache的鼻祖了。另外此时的一致性协议采用了MESI缓存一致性协议。

但是此时L2 Cache还是外部的,后面的Pentium Pro才把L2放到CPU内部,到此为止,就确定了现代缓存的基本模式,并且一直沿用至今。

双核上的L2 Cache

来到双核时代之后,Intel双核心CPU陆续推出了Pentium D、Pentium EE、Core Duo,其中Pentium D、Pentium EE的CPU内部两个内核具有互相独立的二级缓存,不是共享的呀。所以两个CPU核之间的缓存数据同步是依靠北桥芯片上的仲裁单元通过前端总线在两个核心之间传输来实现的,延迟还比较大。

多核共享L2 Cache

双核CPU中的Core Duo在二级缓存上有了巨大突破,就是两个核共享2MB的二级缓存,使用Intel的“Smart cache”共享缓存技术,实现了真正意义上的缓存同步,极大发挥了二级缓存的作用。

现在Cache

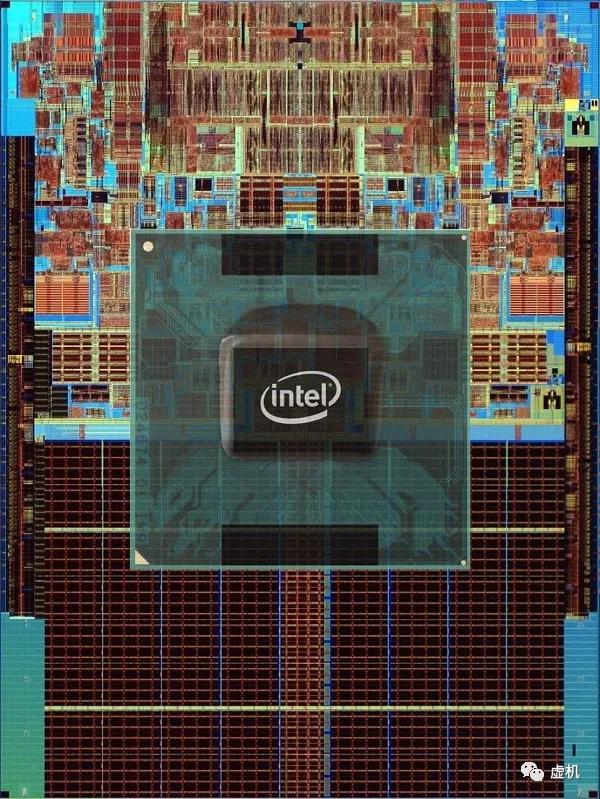

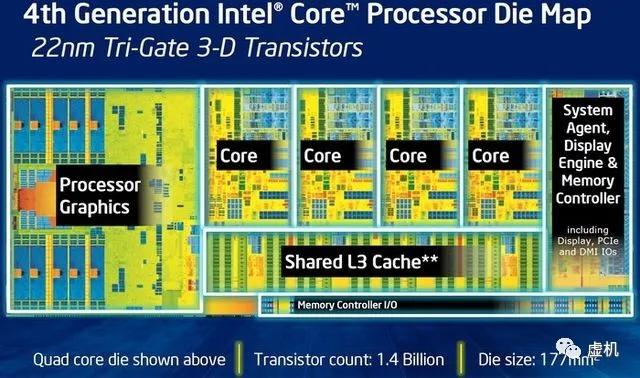

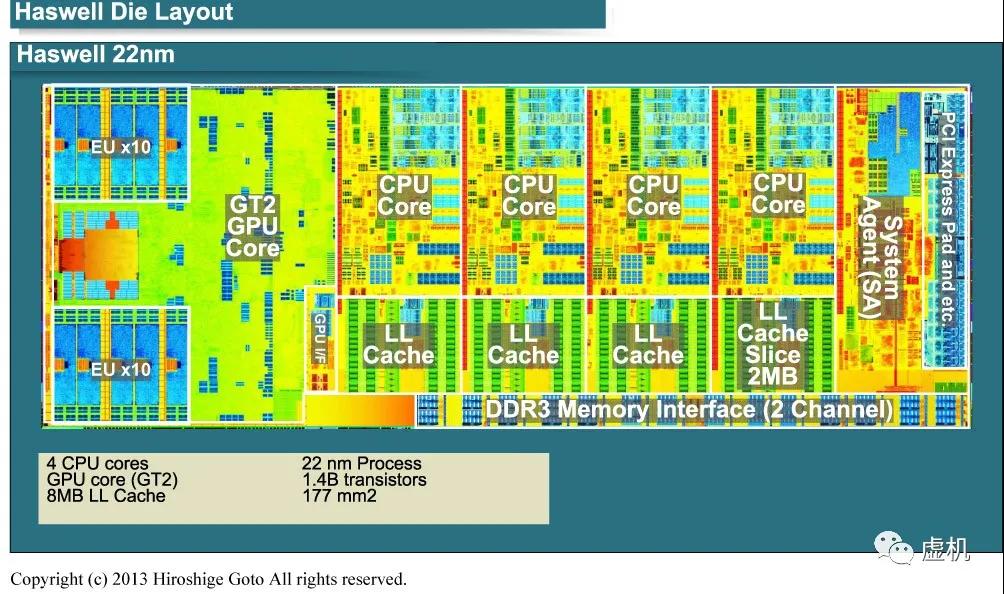

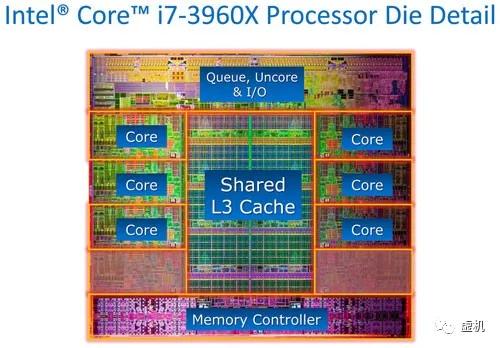

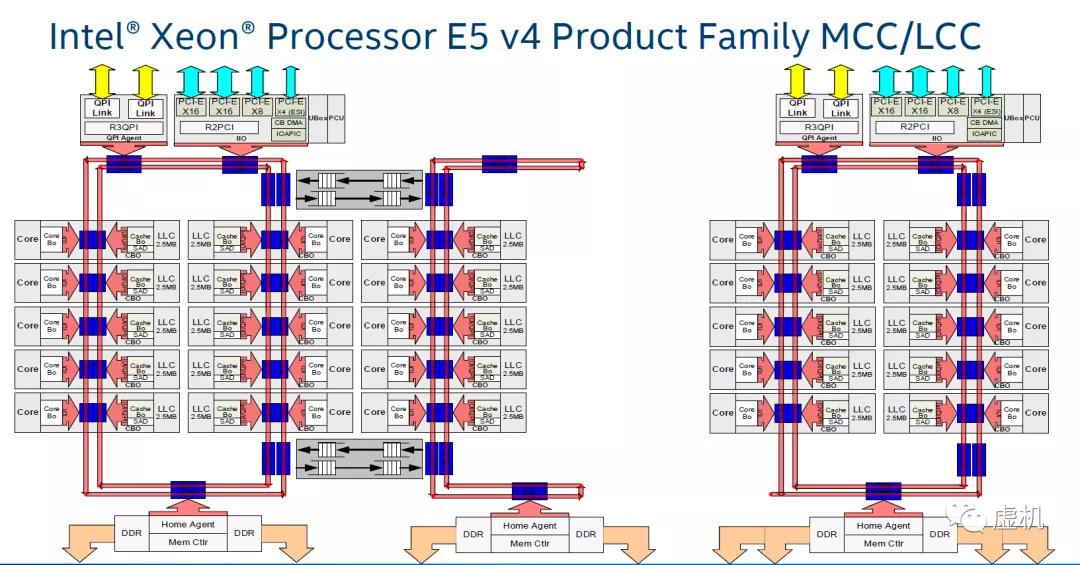

现在CPU都有L3 Cache,一般是多核共享模式,而L2则被每个核单独占据。这时L2也叫做MLC(Middle Level Cache),而L3被叫做LLC(Last Level Cache)。最后我们看看几个典型的Cache设计图:

了解了高速缓存的历史基本就能窥出一点CPU的设计历史。