英特尔(Intel)首席执行官Pat Gelsinger已经受够了…他代表Intel宣布,10纳米工艺还是10纳米,但是该节点(代号SuperFin)的下一代,会叫做“Intel 7”,然后再来是“Intel 4”、“Intel 3”,不会出现“纳米”这个字眼。而在3之后,Intel着眼于埃米(angstroms,Å)尺寸,接下来的节点会叫做“20A”与“18A”。

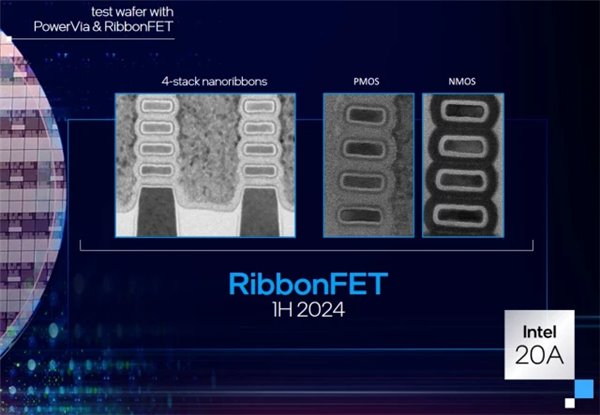

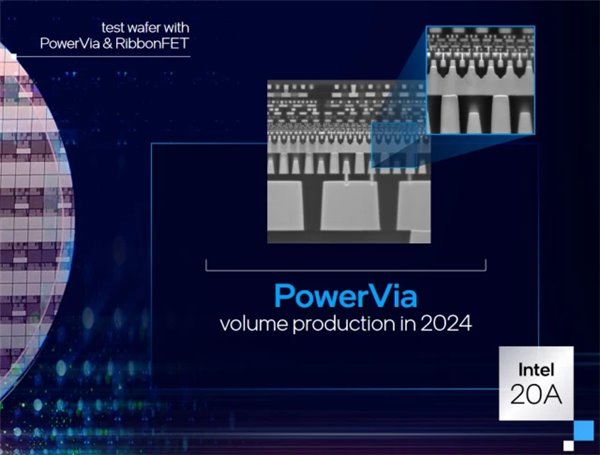

以上是5个工艺节点就是Intel到2025年的技术蓝图,该公司也发表了新晶体管架构──Intel称为“RibbonFET”的一种环绕式栅极(gate all-around,GAA)晶体管变体,还有利用晶圆片背面、命名为PowerVia的新型互连技术;同时,该公司亦宣布正与ASML合作,对极紫外光微(EUV)微影技术的革新做出贡献。

工艺节点的重新命名,也许看来像是一家尝试让所有人忘记他们曾经跌跌撞撞、一度曾失去领导地位的公司在一本正经地胡说八道,但是其竞争对手所使用的节点名称,却会让Intel听起来很“落伍”,更几乎是无意义的营销…所以为何他们不能重新设定命名方法?

Intel一直强调,在任何既定的技术节点上,该公司的产品性能会比其他竞争对手推出的同类产品性能更好;例如其10纳米工艺相当于台积电(TSMC)的7纳米工艺。对IC设计业者来说,性能是一个关键议题,每一代工艺节点的性能需要有所提升,节点之间的进展速度也要加快。然而,众所周知Intel错过了自己订下的10纳米工艺节点量产时程(现在已经全面量产)。

失去(或被认为失去)技术领导地位已经够糟了,在工艺节点的进展路程中跌跌撞撞也很惨、甚至更不好。一家芯片制造商的客户各自有产品蓝图,如果他们的供应伙伴让他们无法达到默认的目标,对他们来说就是考虑换一家新伙伴的时候了。

这解释了为何Gelsinger自从接手Intel首席执行官,就一再宣示该公司将开始按照常规节奏推进每一代工艺节点,而且每一代节点在性能上都会有显著的性能提升。能否按时交货至关重要,如果Intel又遭遇一次无法按时完成工艺节点演进的错误,恐怕不只危及现有客户关系,对该公司力推的全新晶圆代工业务Intel Foundry Services (IFS)也会是致命打击。

Intel在日前举办的全球记者会上宣布了详细的工艺技术蓝图:

Intel 7将于今年问世,并于2022年量产;

Intel 4将于2022年底问世,并于2023年量产;

Intel 3将于2023年稍晚问世,意味着将于2024年量产;

Intel 20A将于2024年初问世;

Intel 18A预计于2025年初问世。

此外Intel也列出了对应以上工艺节点的处理器产品蓝图。举例来说,Intel 7工艺将用于生产2021年客户端设备Alder Lake处理器,以及预计2022年量产的Sapphire Rapids数据中心处理器。Intel 4则将用以生产客户端处理器Meteor Lake,以及数据中心处理器Granite Rapids

Intel表示,其Intel 4工艺将全面采用EUV微影;该公司将继续优化FinFET技术至Intel 3,从20A工艺开始则将转换至GAA晶体管架构。而尽管业界几乎所有开发先进工艺节点的厂商都在期待由FinFET转向GAA,Intel自家的GAA技术被命名为RibbonFET,如下图所示。

积极重夺制造霸主地位,英特尔不玩 “纳米游戏”了

此外Intel也提及了新互连技术PowerVia (参考下图)。该公司表示,传统上互连导线是放置于晶体管顶端,虽然一直以来运作良好,但在新架构更小尺寸上,其效率也随之降低。PowerVia是将互连放置于芯片下方,计划于Intel 3工艺开始试验,预计将于Intel 20A准备好商业化。

积极重夺制造霸主地位,英特尔不玩 “纳米游戏”了

Intel表示正与Qualcomm合作,以20A工艺开发主流智能手机芯片平台;如果合作一切顺利,Qualcomm的背书会发挥重要作用。Intel已经尝试在智能手机市场站稳脚跟好一段时间,但成效不彰。

而为了表明对发展制造技术的承诺,Intel也宣布正与设备业者ASML合作,定义、建立与部署更精练的高数值孔径(high-NA) EUV技术,并声称该公司将会是业界首家量产高数值孔径EUV系统的业者,其该系统将在18A工艺节点为RibbonFET的改善做出贡献。

多年来,Intel一直标榜自家在新一代封装技术方面处于领先地位,而封装技术对于半导体组件性能的进一步提升扮演关键角色。该公司表示,其IFS部门已经与云端巨擘AWS签署合作协议,后者将成为其先进封装技术的第一位客户。

节点命名方式

历史上,最小晶体管栅极与工艺节点命名之间通常存在某种程度关系;但是当这两者之间的关系完全被打破,就会产生一些争议。有人说,那是发生在大约2010年问世的32纳米节点,而Intel则表示应该要追溯至1997年,当时半导体工艺微缩至0.18微米。无论最小晶体管栅极与节点命名之间的距离是何时越拉越远,现在两者之间已经没有关系。

市场研究机构Tirias Research分析师Keven Krewell表示,这也就是为何“工艺节点数字的重设已经逾时;Intel一直在做14纳米+++的东西,但这对Intel以外的其他人来说是没有意义的。台积电则是创建了像是8纳米这样的中间节点,而这意味着很难将晶体管与晶体管进行详细的比较。”

针对Intel在接下来5个节点的规划,Krewell则表示:“该技术蓝图相当激进,但Intel感觉他们已经准备好迎接这样的大跃进;每一个新节点都绑了特定产品,所以Intel的表现如何将会是清晰可见的。而Qualcomm采用20A工艺还是未来几年之后的事,该公司愿意公开承认令人印象深刻;”他也指出,封装技术是很重要的一个讯息,特别是Intel赢得AWS这家客户。

在Intel于美国时间7月26日下午举行的该场记者会上,Gelsinger在接受媒体提问时,被问到了AWS与Qualcomm以外的其他客户。对此,他表示与Qualcomm的合作证明IFS客户将会同步取得与Intel以内部使用为目的所开发、最先进的制造技术;而在Qualcomm之外,该公司也正在与其他客户洽谈,但不方便透露任何名称。

Gelsinger仅透露,那些客户有的来自工业领域,有的来自汽车领域,也有的是需要代工伙伴的半导体业者──包括一些在传统上是竞争对手的厂商;他充满热情地表示:“IFS已经投入竞赛!”