现代的CPU基本上归为冯诺伊曼结构(也成普林斯顿结构)和哈佛结构。

冯洛伊曼结构就是我们所说的X86架构,而哈佛结构就是ARM架构。一个广泛用于桌面端(台式/笔记本/服务器/工作站等),一个雄踞移动领域,我们的手持设备(平板\手机用的大多就是他了)。

01冯·诺依曼体系

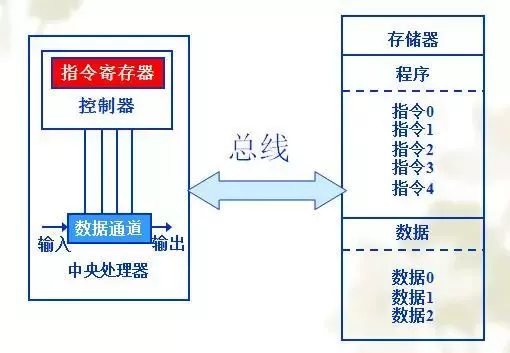

冯·诺依曼体系结构图如下

冯·诺依曼体系的特点:

A、数据与指令都存储在同一存储区中,取指令与取数据利用同一数据总线。

B、被早期大多数计算机所采用。

C、ARM7——冯诺依曼体系结构简单,但速度较慢。取指不能同时取数据

冯·诺依曼结构也称普林斯顿结构,是一种将程序指令存储器和数据存储器合并在一起的存储器结构。程序指令存储地址和数据存储地址指向同一个存储器的不同物理位置,因此程序指令和数据的宽度相同,如英特尔公司的8086中央处理器的程序指令和数据都是16位宽。

冯.诺依曼结构处理器具有以下几个特点:

1:必须有一个存储器;

2:必须有一个控制器;3:必须有一个运算器,用于完成算术运算和逻辑运算;4:必须有输入设备和输出设备,用于进行人机通信。另外,程序和数据统一存储并在程序控制下自动工作。冯·诺依曼结构:

英特尔公司的8086。英特尔公司的其他中央处理器。ARM的ARM7。MIPS公司的MIPS处理器。

02哈佛体系

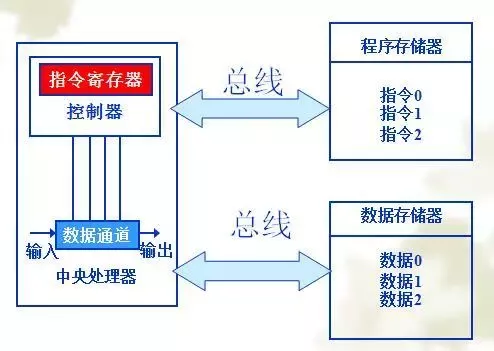

哈佛体系结构图

结构特点:

A、程序存储器与数据存储器分开.

B、提供了较大的存储器带宽,各自有自己的总线。

C、适合于数字信号处理.

D、大多数DSP都是哈佛结构.

E、ARM9是哈佛结构,取指和取数在同一周期进行,提高速度,改进哈佛体系结构分成三个存储区:程序、数据、程序和数据共用。

哈佛结构是一种存储器并行体系结构,主要特点是将程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个独立的存储器,每个存储器独立编址、独立访问。程序指令存储和数据存储分开,可以使指令和数据有不同的数据宽度。

哈佛结构能基本上解决取指和取数的冲突问题.而对另一个操作数的访问,就只能采用Enhanced哈佛结构了,例如像TI那样,数据区再split,并多一组总线.或向AD那样,采用指令cache,指令区可存放一部分数据.。

哈佛结构:

1、ARM(除arm7)

2、大部分DSP

哈佛体系架构有个致命的弱点在动态加载程序上面,想象我们从外存中读取一段程序然后加载到RAM,这个程序是在数据内存当中的,我们需要一种机制将数据内存再传输到程序内存当中去,这反而增加了设备复杂度。

对于多任务操作系统来说,管理程序内存是一件非常重要的事情,而且仅仅是保护模式下的页面映射等等机制就已经足够复杂了,如果还要求将程序和数据分开管理,复杂度就太高了。这种时候冯诺依曼体系结构就有非常大的优势了。

03arm和哈佛、冯·诺依曼的关系

哈佛架构是针对cpu从cache中取指而言,指令和数据在主存中并未分开,但在加载到cache中的时候被分离为指令和数据两份存储空间,cpu可以同时从cache取到指令和数据.

所以arm系统CPU(除arm7)对外表现为冯.诺伊曼架构,对内则表现为哈佛架构。

04实际芯片制造

实际上,绝大多数现代计算机使用的是所谓的“ModifiedHarvard Architecture”,指令和数据共享同一个address space,但缓存是分开的。可以说是两种架构的一种折中吧。

在现实世界中很少有非常纯粹的概念,特别是在实际的应用里。教科书里的大多是理想化的模型,便于掌握某个概念的重点和本质,但实际中很难达到这种理想化的状态。

哈佛结构和冯诺依曼结构主要区别在是否区分指令与数据。在教科书里这是两种截然不同的做法。

但实际上在内存里,指令和数据是在一起的。而在CPU内的缓存中,还是会区分指令缓存和数据缓存,最终执行的时候,指令和数据是从两个不同的地方出来的。你可以理解为在CPU外部,采用的是冯诺依曼模型,而在CPU内部用的是哈佛结构。

大部分的DSP都没有缓存,因而直接就是哈佛结构。

哈佛结构设计复杂,但效率高。冯诺依曼结构则比较简单,但也比较慢。CPU厂商为了提高处理速度,在CPU内增加了高速缓存。也基于同样的目的,区分了指令缓存和数据缓存。有时为了解决现实问题,究竟是什么主义真的没那么重要。因而个人认为争论到底是哪种结构意义不大。