本文转载自微信公众号「智能计算芯世界」,作者synopsys 。转载本文请联系智能计算芯世界公众号。

目前支持AI计算开发的半导体有独立加速器和 in-memory/near-memory 计算技术两种。独立加速器以某种方式连接到应用处理器,并且有一些应用处理器在设备上添加了神经网络硬件加速。独立加速器可以通过芯片与芯片的互连而实现了将硬件扩展到多个芯片的巨大创新,从而实现最高性能,in-memory 和 near-memory 计算技术主要满足减少能耗需求。

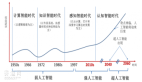

设备上的 AI 加速正在通过利用处理器和架构对他们的神经网络处理器进行升级,这些处理器和架构是独立半导体的先驱。半导体领导者、行业巨头和数百家初创公司都在全力将 AI 能力推广到各个行业的大量新型 SoC 和芯片组中,涵盖从云服务器组到每个厨房中的家庭助理等所有环节。

深度学习神经网络用在许多不同的应用中,为使用它们的人提供了强大的新工具。例如,它们可以用于高级安全威胁分析、预测和预防安全漏洞,以及通过预测潜在买家的购物流程而帮助广告商识别和简化销售流程。这是在融合最新 GPU 和 AI 加速器半导体技术的服务器群中运行的数据中心应用的两个实例。

但 AI 设计并未包含在数据中心内。许多新功能可基于传感器输入的组合而了解发生的情况,例如用于对象和面部检测的视觉系统,用于改进人机接口的自然语言理解以及上下文感知)。这些深度学习能力已添加到所有行业的 SoC 中,包括汽车、移动、数字家庭、数据中心和物联网 (IoT)。

为实现最高性能,针对云 AI 加速的 SoC 设计人员致力于最大限度地提升性能以解决重大问题。执行 AI 训练以及为了得到最高准确度而需要的最复杂的 AI 算法,需要很高的处理器运算能力(TOPS),这最终可通过缩短训练时间而降低成本,并减少推理过程所需的能耗。云计算市场的这些半导体硬件创新使人们认为可能需要花费数年开发才能完成的工作成为可能,并缩短了取得突破的时间,例如,以识别和疫苗开发的形式找到当前最令人担忧的健康问题的治疗方法。

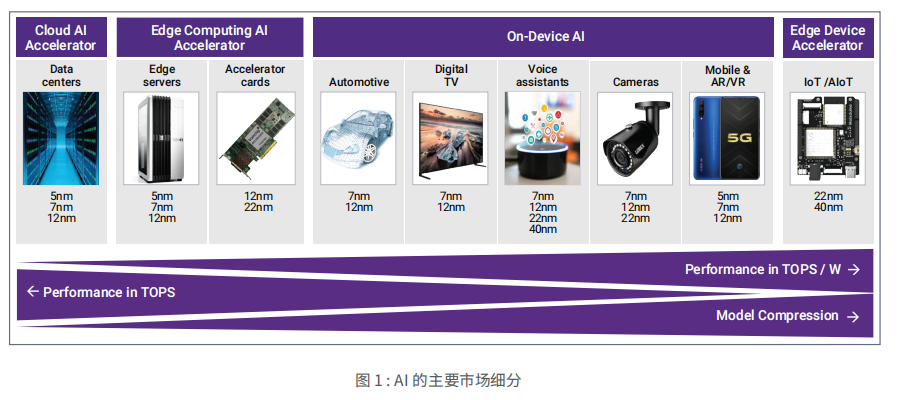

然而,并非所有问题都可以在云端解决,因此,许多 AI 加速器架构经过修改,可支持边缘计算和设备端 AI。在边缘服务器和插入式加速卡中,成本和功耗更加重要。随着我们越来越靠近并进入数据收集点的应用“边缘设备加速器”,单位能耗性能的优化成为最高设计要求。

边缘设备加速器的资源、处理和内存有限,因此,经过训练的算法需要压缩和裁剪,以满足功耗和性能的要求,同时保证所需的准确性。最大的 AI 细分市场是设备端 AI,它会影响多种应用,例如汽车 ADAS、数字电视的超高图像分辨率、音频和语音识别以及智能音箱中的语言理解。这类应用包括执行面部检测、面部识别和物体识别的摄像头。

例如,在某些行业中,摄像头中的设备端 AI 可对工业应用执行缺陷分析。设备端 AI 类别还包括消费类应用,例如手机和 AR/VR 耳机,这些应用可实现前面提到的许多AI 功能,例如导航、超高图像分辨率、语音理解、对象 / 面部检测等,而且所有这些都在小巧的体积中实现。移动设备通过最新的工艺节点而持续在工艺中保持领先地位,这与用于云计算的工艺节点类似。边缘和设备端计算不断优化性能。根据市场的不同,可以采用传统工艺节点。

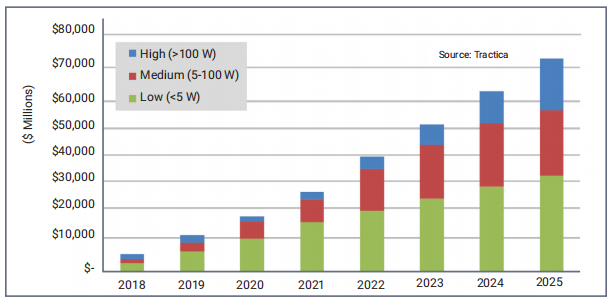

2020 年,AI 市场仍处于初期阶段,并有望在未来几年内快速增长。大于 100W 的云 AI SoC 厂商包括市场领导者NVIDIA 和 Intel。通过先发优势,这些厂商占据了主导地位。大量初创企业希望在效率方面比这些解决方案高出多倍。此外,Google、TPU、阿里巴巴、亚马逊和百度等系统公司也设计自己的芯片,并通过优化而支持其业务模式。所有这些公司都为客户提供云出租服务,使客户能够在云端进行培训和推理。

边缘计算 (>5W) SoC 通常利用现有的云解决方案,或者经过修改的云架构,但是许多初创企业通过更低功耗和更优化的解决方案而找到了自己的市场位置,同时在性能上远远超越当今的解决方案。

在图2 中,5W 以下市场包括设备端和独立加速器,通常称为 AIoT 加速器,这一市场正在迅速发展。对于设备端解决方案,移动市场在出货量方面占主导地位,而汽车市场也在快速增长,例如 Tesla ASIC。在低于 5W 的市场中,AIoT 加速器仍然只占很小的比例,但 Perceive、Kneron、Gyrfalcon、Brainchip 和 GrAI Matter Labs 等公司都在试图突围。

每个 AI 市场细分都有不同的目标和挑战。云 AI SoC 设计人员注重缩短昂贵的训练时间,同时适应可包含 80 亿个甚至更多参数的最复杂的新算法。边缘计算 AI 设计更注重降低功耗和延迟。5G 和设备端 AI 旨在实现低延迟,但对于 5G,这些 AI 并不用于压缩模型,因为这可能是非常昂贵且耗时的设计过程。对于设备端 AI,您需要通过压缩模型,最大程度优化功能和性能的推理。

最后,AIoT独立加速器设计人员使用更多创新技术,并且往往是 TOPS/W 的领导者。在提高密度,缩短延迟,以及应对存储系数的波动方面,他们承担着更多的风险,而且他们还是裁剪和压缩算法以及为客户实施算法的专家,提供了独特的差异化能力。

除这些独特的挑战外,AI 市场也面临着一系列核心挑战,包括:

添加专门的处理能力,可以更高效地执行必要的数学运算,例如矩阵乘法和点积

高效的内存访问,可处理深度学习所需的唯一系数,例如权重和激活

可靠且经过验证的实时接口,用于芯片到芯片、芯片到云端、传感器数据以及加速器到主机的连接

保护数据并防止黑客攻击和数据损坏

AI 模型使用大量内存,这增加了芯片的成本。训练神经网络可能需要几 GB 到 10 GB 的数据,这需要使用最新的 DDR 技术,以满足容量要求。例如,作为图像神经网络的 VGG-16 在训练时需要大约 9GB 的内存。更精确的模型 VGG-512 需要 89GB 的数据才能进行训练。为了提高 AI 模型的准确性,数据科学家使用了更大的数据集。同样,这会增加训练模型所需的时间或增加解决方案的内存需求。

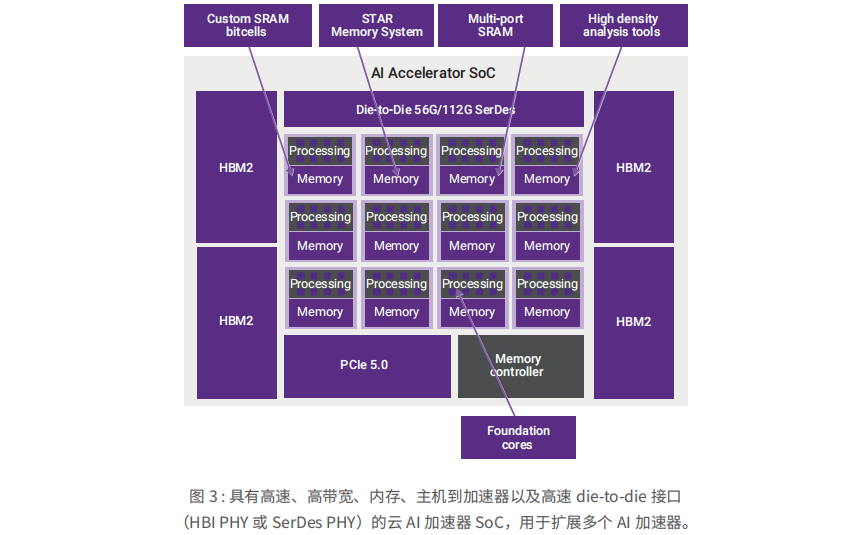

由于需要大规模并行矩阵乘法运算以及模型的大小和所需系数的数量,这需要具有高带宽存取能力的外部存储器。新的半导体接口 IP,如高带宽存储器 (HBM2) 和未来的衍生产品 (HBM2e),正被迅速采用,以满足这些需求。先进的 FinFET 技术支持更大的片上 SRAM 阵列和独特的配置,具有定制的存储器到处理器和存储器到存储器接口,这些技术正在开发中,目的是更好地复制人脑并消除存储器的约束。

AI 模型可以压缩。这种技术是确保模型在位于手机、汽车和物联网应用边缘的 SoC 中受限的存储器架构上运行所必需的。压缩采用剪枝(pruning)和量化(pruning)技术进行,而不降低结果的准确性。这使得传统 SoC 架构(具有 LPDDR 或在某些情况下没有外部存储器)支持神经网络,然而,在功耗和其他方面需要权衡。随着这些模型的压缩,不规则的存储器存取和不规则的计算强度增加,延长了系统的执行时间和延迟。因此,系统设计人员正在开发创新的异构存储器架构。

AI SoC设计解决方案

在SoC中添加 AI 功能突显了当今 SoC 架构在 AI 方面的薄弱。在为非 AI 应用构建的 SoC 上实施视觉、语音识别和其他深度学习和机器学习算法时,资源非常匮乏。IP 的选择和集成明确界定了 AI SoC 的基准效率,这构成了 AI SoC 的“DNA”,或者叫先天性。例如,引入定制处理器或处理器阵列可以加速 AI 应用中所需的大规模矩阵乘法。

云AI加速器

为了应对带宽和可靠性挑战,云 AI 加速器 SoC 设计人员正在集成 HBM2e 和 HBM3,以及用于芯片到芯片通信的高速 SerDes die-to-die 或 PCIe。安全(包括支持 AI 模型加密和身份验证的高速安全协议加速器)的作用越来越明显。嵌入式内存解决方案的多端口存储器 (TCAMs) 与 SRAM 编译器一起有助于减少泄漏。

边缘计算AI 加速器

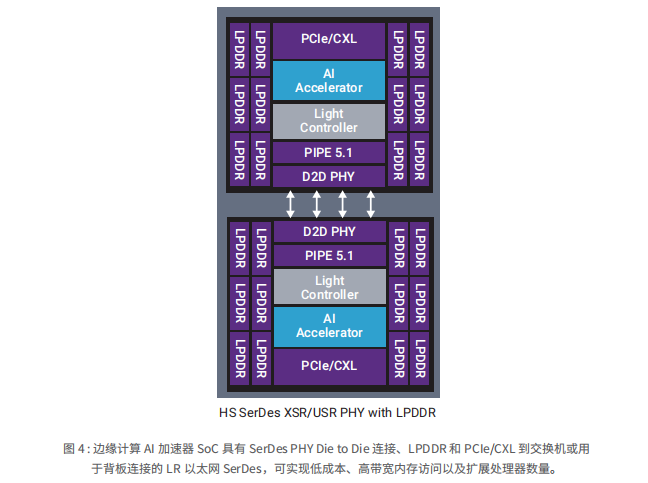

许多边缘计算应用的主要目标是围绕与较低延迟相关的新服务。为了支持较低的延迟,许多新系统都采用了一些最新的行业接口标准,包括 PCIe 5.0、LPDDR5、DDR5、HBM2e、USB 3.2、CXL、基于 PCIe 的 NVMe 以及其他基于新一代标准的技术。与上一代产品相比,每一种技术都通过增加带宽而降低延迟。

比减少延迟的驱动因素更为突出的是为所有这些边缘计算系统增加 AI 加速。AI 加速由某些服务器芯片通过 x86 扩展 AVX-512 向量神经网络指令 (AVX512 VNNI) 等新指令提供,或者提供给移动应用处理器,例如高通 DSP 内核。很多时候,这种额外的指令集不足以提供预期任务所需的低延迟和低功耗,因此,大多数新系统中还添加了定制 AI 加速器。这些芯片所需的连接能力通常采用带宽最高的主机而实现加速器连接。例如,由于这些带宽要求直接影响延迟,PCIe 5.0 正迅速得到广泛的应用,最常见的是用在具有多个 AI 加速器的某种交换配置中。

CXL 是另一种为降低延迟并提供缓存一致性而专门开发的接口,正迅速兴起。由于 AI 算法具有异构计算需求和大量内存需求,因此,确保缓存一致性至关重要。

除了本地网关和聚合服务器系统之外,单个 AI 加速器通常无法提供足够的性能,因此需要借助带宽极高的芯片到芯片的 SerDes PHY 而扩展这些加速器。最新发布的 PHY 支持 56G 和 112G 连接。支持 AI 扩展的芯片到芯片要求已经在多个项目中实施。在基于标准的实施项目中,以太网可能是一种可扩展的选项,现在已经推出了一些基于这种理念的解决方案。然而,当今许多实施项目都是通过专有控制器而利用最高带宽的 SerDes。不同的架构可能会改变服务器系统的未来 SoC 架构,从而将网络、服务器、AI 和存储组件整合到集成度更高的 SoC 中,而不是目前实施的 4 种不同 SoC 中。

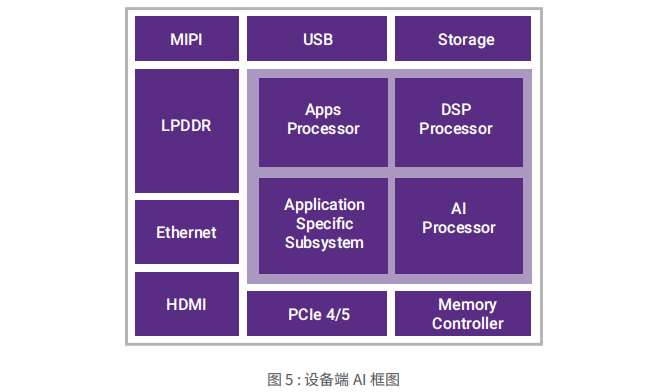

设备端AI

关于设备端 AI 处理的一个最大关注点就是软件能力。算法变化很快。设计人员需要采用 Tensorflow 和 Caffe 等传统工具训练初始模型,然后将其映射到设备上的处理器。借助可针对特定处理器进行优化并保持高精度的图形映射工具,以及进行压缩和修剪的工具,许多工程可以节省数月的时间和精力。如果没有这些工具,软件和系统的设计速度赶不上硬件的设计。

优化的内存配置可以优化设备端 AI 系统。在开始设备本身的架构设计之前,设计人员需要拥有可模拟多个 IP 权限和配置的工具。在运行实际算法的同时,通过利用处理器模拟片上和片外存储器,可以在开始设计之前为设计人员提供最有效的架构。由于有些设计人员尚不清楚如何优化系统,因此,他们经常需要为同一过程节点开发多代产品,这会浪费数月的时间。

最后,传感器连接对于设备端 AI 系统的视觉至关重要。MIPI CSI-2 是 CMOS 图像传感器的最常见实施。新的 V3 规范旨在提高机器感知能力,并支持更高的精度,从而提供更高质量的图像。特别需要指出的是,智能化能力应有助于提高效率,因为新数据仅在需要时才提供,而不是提供整个图像。I3C 整合了多个传感器,为支持多个系统输入源提供了一种低成本的方法。

随着 AI 能力进入新市场,选择用于集成的 IP 为 AI SoC 提供了关键组件。但除了 IP 之外,设计人员还发现,利用 AI 专业知识、服务和工具具有明显的优势,能够确保设计的按时交付,为最终客户提供高质量的服务和高价值,以满足新的创新应用需求。