本文基于三星Cortex-A9架构,Exynos4412讲解I2C原理、以及基于I2C的mpu6050陀螺仪的数据读取实例(包括在裸机模式下数据的读取以及基于Linux驱动的读取)。还会分析Linux内核I2C架构,篇幅过长,绝对干货。

裸机篇

本篇首先详细讲解I2C时序,然后讲解如何基于三星I2C控制实现裸机读取从设备信息方法。

前言

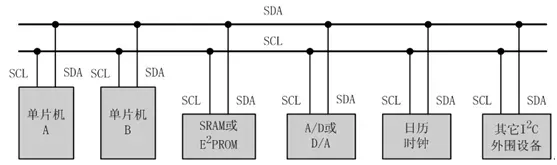

I2C(Inter-Integrated Circuit)总线(也称 IIC 或 I2C) 是有PHILIPS公司开发的两线式串行总线,用于连接微控制器及外围设备,是微电子通信控制领域广泛采用的一种总线标准。它是同步通信的一种特殊形式,具有接口线少、控制方式简单、器件封装形式小、通信速率较高等优点。

Exynos4412 i2c控制器综述

Exynos4412精简指令集微处理器支持4个IIC总线控制器。为了能使连接在总线上的主和从设备之间传输数据,专用的数据线SDA和时钟信号线SCL被使用,他们都是双向的。

如果工作在多主机的IIC总线模式,多个4412处理器将从从机那接收数据或发送数据给从机。在IIC总线上的主机端4412会启动或终止一个数据传输。4412的IIC总线控制器会用一个标准的IIC总线仲裁机制去实现多主机和多从机传输数据。

通过控制如下寄存器以实现IIC总线上的多主机操作:

- 控制寄存器: I2CCON

- 状态寄存器: I2CSTAT

- Tx/Rx数据偏移寄存器:I2CDS

- 地址寄存器: I2CADD

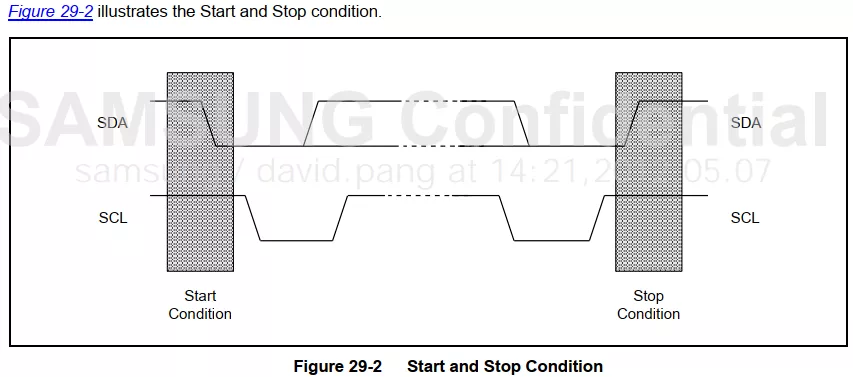

如果I2C总线空闲,那么SCL和SDA信号线将都为高电平。在SCL为高电平期间,如果SDA有由高到低电平的跳变,那么将启动一个起始信号,如果SDA有由低到高电平的跳变,将启动一个结束信号。

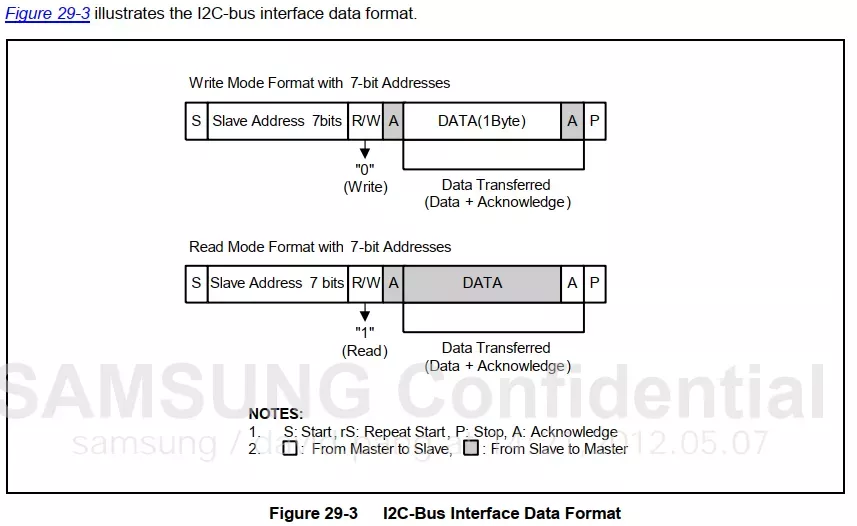

主机端的设备总是提供起始和停止信号的一端。在起始信号被发出后,一个数据字节的前7位被当作地址通过SDA线被传输。这个地制值决定了总线上的主设备将要选择那个从设备作为传输对象,bit8决定传输数据的方向(是读还是写)。

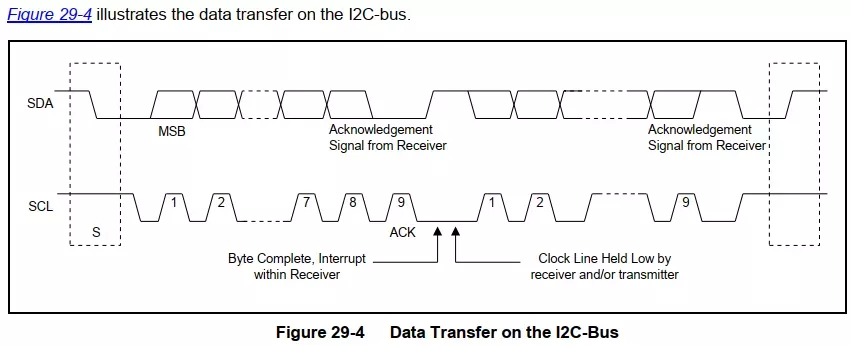

I2C总线上的数据(即在SDA上传输的数据)都是以8位字节传输的,在总线上传输操作的过程中,对发送或接收的数据字节数是没有限制的。I2C总线上的主/从设备发送数据总是以一个数据的最高位开始传输(即MSB方式),传输完一个字节后,应答信号紧接其后。

Exynos4412 I2C总线接口特性

- 共有9个通道,支持多主、从I2C总线接口。其中8个通道作为普通接口(即I2C0、I2C1....),1个通道作为HDMI的专用接口。

- 7位地址模式。

- 串行,8位单向或双向的数据传输。

- 在标准模式中,每秒最多可以传输100k位,即12.5kB的数据量。

- 在快速模式中,每秒最多可以传输400k位,即50kB的数据量。

- 支持主机端发送、接收,从机端发送、接收操作。

- 支持中断和查询方式。

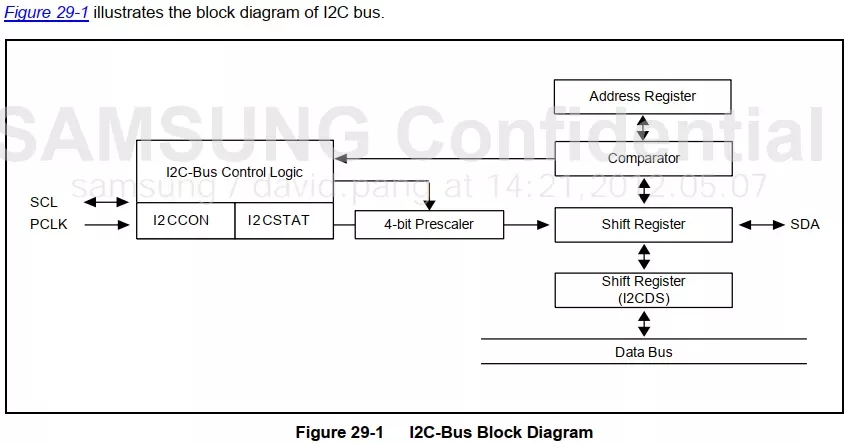

框图

从上图可以看出,4412提供4个寄存器来完成所有的IIC操作。SDA线上的数据从IICDS寄存器经过移位寄存器发出,或通过移位寄存器传入IICDS寄器;IICADD寄存器中保存4412当做从机时的地址;IICCON、IICSTAT两个寄存器用来控制或标识各种状态,比如选择工作工作模式,发出S信号、P信号,决定是否发出ACK信号,检测是否接收到ACK信号。

I2C总线接口操作

针对4412处理器的I2C总线接口,具备4种操作模式:

- 主机发送模式

- 主机接收模式

- 从机发送模式

- 从机接收模式

下面将描述这些操作模式之间的功能关系:

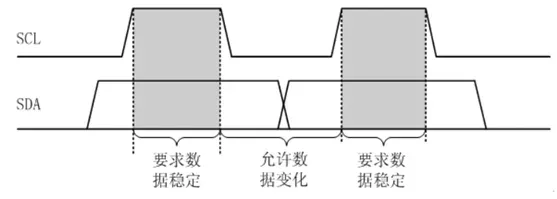

0、数据有效性

在这里插入图片描述

SDA线上的数据必须在时钟的高电平周期保持稳定。数据线的高或低电平状态IIC位传输数据的有效性在SCL线的时钟信号是低电平才能改变。

1. 开始和停止条件

当4412的I2C接口空闲时,它往往工作在从机模式。或者说,4412的的i2c接口在SDA线上察觉到一个起始信号之前它应该工作在从机模式。当控制器改变4412的i2c接口的工作模式为主机模式后,SDA线上发起数据传输并且控制器会产生SCL时钟信号。

开始条件通过SDA线进行串行的字节传输,一个停止信号终止数据传输,停止信号是指SCL在高电平器件SDA线有从低到高电平的跳变,主机端产生起始和停止条件。当主、从设备产生一个起始信号后,I2C总线将进入忙状态。这里需要说明的是上述主从设备都有可能作为主机端。

当一个主机发送了一个起始信号后,它也应该发送一个从机地址以通知总线上的从设备。这个地址字节的低7位表示从设备地址,最高位表示传输数据的方向,即主机将要进行读还是写。当最高位是0时,它将发起一个写操作(发送操作);当最高位是1时,它将发起一个读数据的请求(接收操作)。

主机端发起一个结束信号以完成传输操作,如果主机端想在总线上继续进行数据的传输,它将发出另外一个起始信号和从设备地址。用这样的方式,它们可以用各种各样的格式进行读写操作。

下图为起始和停止信号:

2. 数据传输格式

放到SDA线上的所有字节数据的长度应该为8位,在每次传输数据时,对传输数据量没有限制。在起始信号后的第一个数据字节应该包含地址字段,当4412的I2C接口被设置为主模式时,地址字节应该由控制器端发出。在每个字节后,应该有一个应答位。

如果从机要完成一些其他功能后(例如一个内部中断服务程序)才能继续接收或发送下一个字节,从机可以拉低SCL迫使主机进入等待状态。当从机准备好接收下一个数据并释放SCL后,数据传输继续。如果主机在传输数据期间也需要完成一些其他功能(例如一个内部中断服务程序)也可以拉低SCL以占住总线。

下面的图中将说明数据传输格式:

上图中说明,在传输完每个字节数据后,都会有一个应答信号,这个应答信号在第9个时钟周期。具体过程如下(注意下面描述的读写过程都是针对 4412处理器而言,当有具体的I2C设备与4412相连时,数据表示什么需要看具体的I2C设备,4412是不知道数据的含义的):

写过程:主机发送一个起始信号S→发送从机7位地址和1位方向,方向位表示写→主机释放SDA线方便从机给回应→有从机匹配到地址,拉低SDA线作为ACK→主机重新获得SDA传输8位数据→主机释放SDA线方便从机给回应→从机收到数据拉低SDA线作为ACK告诉主机数据接收成功→主机发出停止信号。

读过程:主机发送一个起始信号S→发送从机7位地址和1位方向,方向位表示读→主机释放SDA线方便从机给回应→有从机匹配到地址,拉低SDA线作为ACK→从机继续占用SDA线,用SDA传输8位数据给主机→从机释放SDA线(拉高)方便主机给回应→主机接收到数据→主机获得SDA线控制并拉低SDA线作为ACK告诉从机数据接收成功→主机发出停止信号。

注意:在具体的I2C通信时,要看I2C设备才能确定读写时序,比如下面即将描述的第七大点中的示例,读写EEPROM中就会说道具体的数据含义,读写过程。

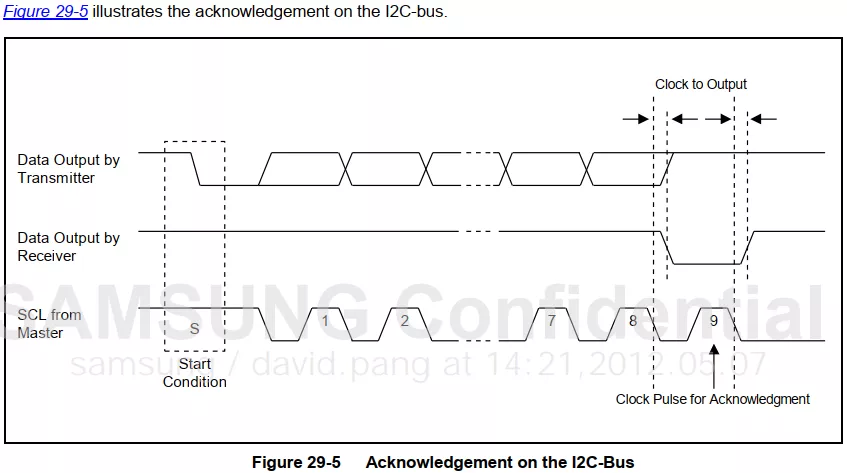

3. 应答信号的传输

为了完成一个字节数据的传输,接收方将发送一个应答位给发送方。应答信号出现在SCL线上的时钟周期中的第九个时钟周期,为了发送或接收1个字节的数据,主机端会产生8个时钟周期,为了传输一个ACK位,主机端需要产生一个时钟脉冲。ACK时钟脉冲到来之际,发送方会在SDA线上设置高电平以释放SDA线。在ACK时钟脉冲之间,接收方会驱动和保持SDA线为低电平,这发生在第9个时钟脉冲为高电平期间。应答信号为低电平时,规定为有效应答位(ACK简称应答位),表示接收器已经成功地接收了该字节;应答信号为高电平时,规定为非应答位(NACK),一般表示接收器接收该字节没有成功。对于反馈有效应答位ACK的要求是,接收器在第9个时钟脉冲之前的低电平期间将SDA线拉低,并且确保在该时钟的高电平期间为稳定的低电平。如果接收器是主控器,则在它收到最后一个字节后,发送一个NACK信号(即不发出ACK信号),以通知被控发送器结束数据发送,并释放SDA线,以便主控接收器发送一个停止信号P。

4. 读写操作

当I2C控制器在发送模式下发送数据后,I2C总线接口将等待直到移位寄存器(I2CDS)接收到一个数据。在往此寄存器写入一个新数据前,SCL线应该保持为低电平,写完数据后,I2C控制器将释放SCL线。当前正在传输的数据传输完成后,4412会捕捉到一个中断,然后cpu将开始往I2CDS寄存器中写入一个新的数据。

当I2C控制器在接收模式下接收到数据后,I2C总线接口将等待直到I2CDS寄存器被读。在读到新数据之前,SCL线会被保持为低电平,读到数据后I2C控制器将释放掉SCL线。一个新数据接收完成后,4412将收到一个中断,cpu收到这个中断请求后,它将从I2CDS寄存器中读取数据。

5. 总线仲裁机制

总线上可能挂接有多个器件,有时会发生两个或多个主器件同时想占用总线的情况,这种情况叫做总线竞争。I2C总线具有多主控能力,可以对发生在SDA线上的总线竞争进行仲裁,其仲裁原则是这样的:当多个主器件同时想占用总线时,如果某个主器件发送高电平,而另一个主器件发送低电平,则发送电平与此时SDA总线电平不符的那个器件将自动关闭其输出级。总线竞争的仲裁是在两个层次上进行的。首先是地址位的比较,如果主器件寻址同一个从器件,则进入数据位的比较,从而确保了竞争仲裁的可靠性。由于是利用I2C总线上的信息进行仲裁,因此不会造成信息的丢失。

6. 终止条件

当一个从接收者不能识别从地址时,它将保持SDA线为高电平。在这样的情况下,主机会产生一个停止信号并且取消数据的传输。当终止传输产生后,主机端接收器会通过取消ACK的产生以告诉从机端发送器结束发送操作。这将在主机端接收器接收到从机端发送器发送的最后一个字节之后发生,为了让主机端产生一个停止条件,从机端发送者将释放SDA线。

7. 配置I2C总线

如果要设置I2C总线中SCL时钟信号的频率,可以在I2CCON寄存器中设置4位分频器的值。I2C总线接口地址值存放在I2C总线地址寄存器(I2CADD)中,默认值未知。

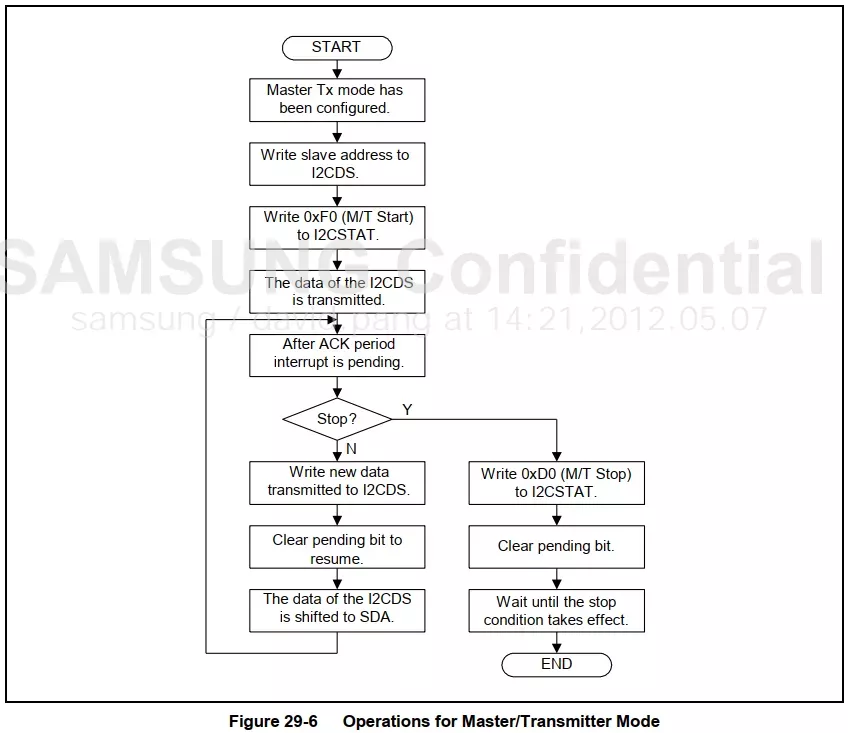

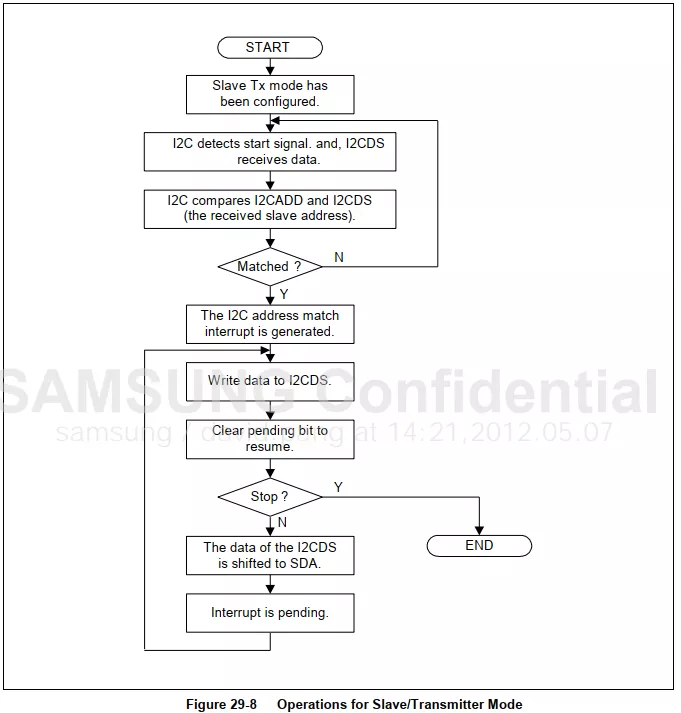

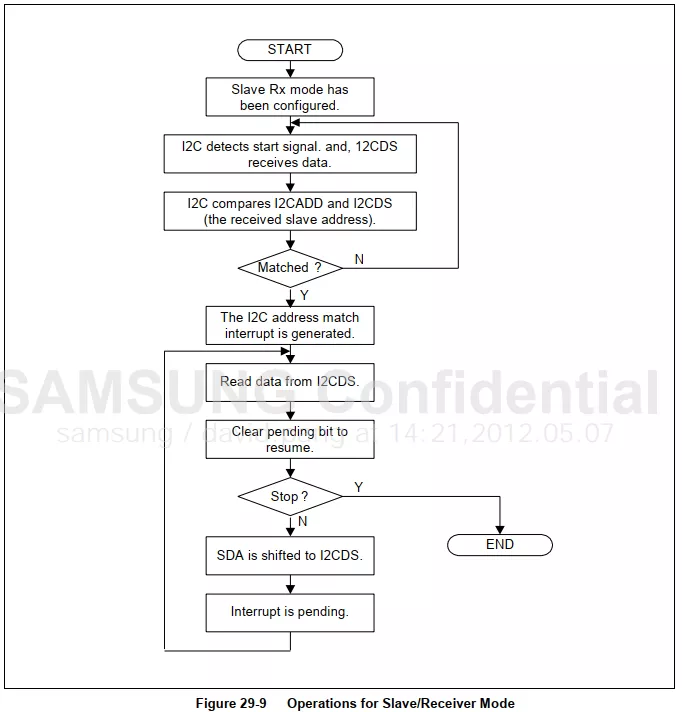

8. 每种模式下的操作流程图

在I2C总线上执行任何的收发Tx/Rx操作前,应该做如下配置:

(1)在I2CADD寄存器中写入从设备地址 (2)设置I2CCON控制寄存器

- a. 使能中断

- b. 定义SCL频率

(3)设置I2CSTAT寄存器以使能串行输出

下图为主设备发送模式

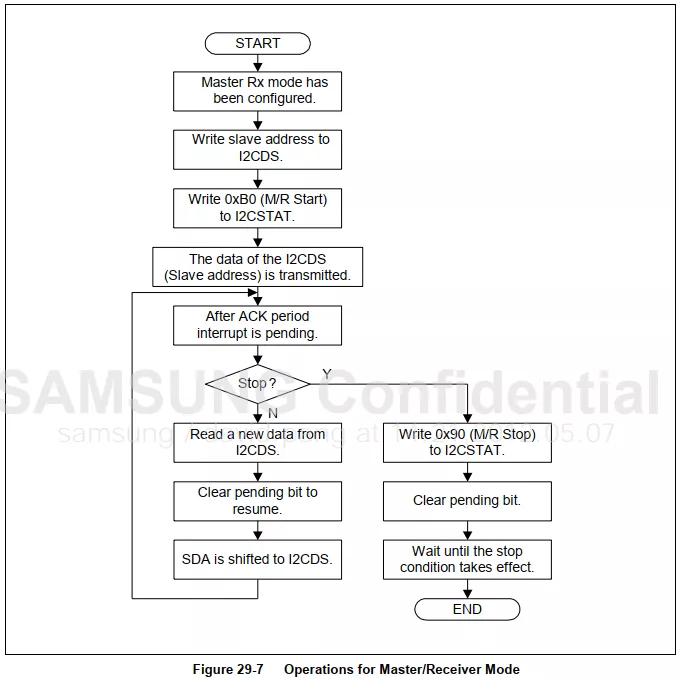

下图为主设备接收模式

下图为从设备发送模式

下图为从设备接收模式

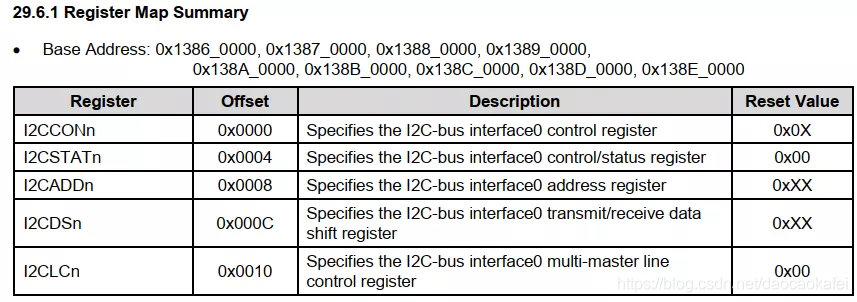

I2C控制器寄存器

I2C控制器用到的寄存器如下所示:

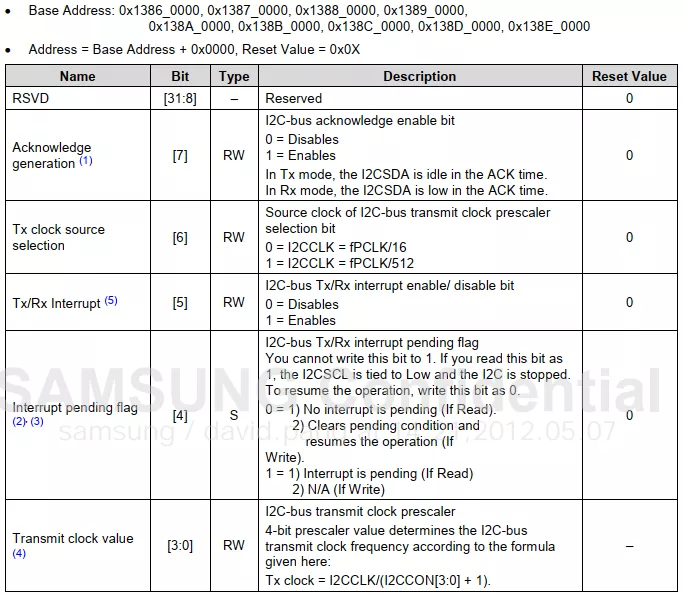

1-- I2C总线控制寄存器

IICCON寄存器用于控制是否发出ACK信号、设置发送器的时钟、开启I2C中断,并标识中断是否发生

使用IICCON寄存器时,有如下注意事项

1.发送模式的时钟频率由位[6]、位[3:0]联合决定。另外,当 IICCON[6]=0时,IICCON[3:0]不能取0或1。

2.位[4]用来标识是否有I2C中断发生,读出为0时标识没有中断发生,读出为1时标识有中断发生。当此位为1时,SCL线被拉低,此时所以I2C传输停止;如果要继续传输,需写入0清除它。

中断在以下3种情况下发生:

- 当发送地址信息或接收到一个从机地址并且吻合时;

- 当总线仲裁失败时;

- 当发送/接收完一个字节的数据(包括响应位)时;

3.基于SDA、SCL线上时间特性的考虑,要发送数据时,先将数据写入IICDS寄存器,然后再清除中断。

4.如果IICCON[5]=0,IICCON[4]将不能正常工作,所以,即使不使用I2C中断,也要将IICCON[5]设为1.

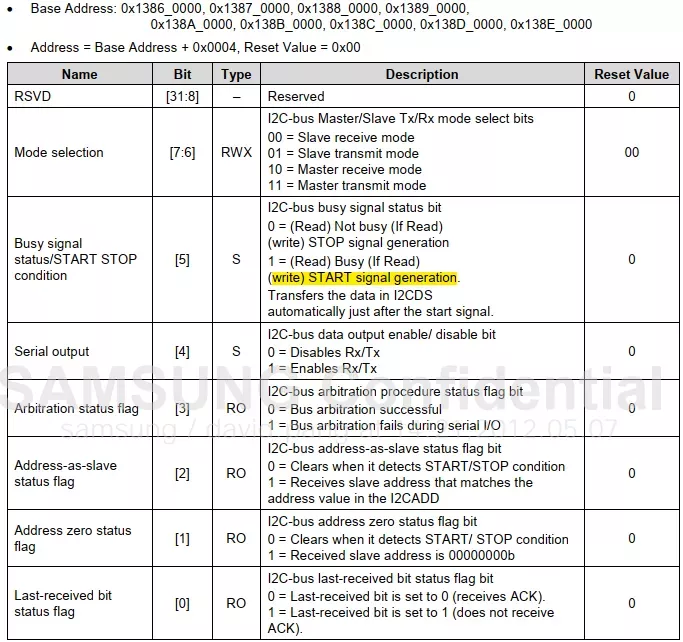

2 -- I2C状态寄存器

IICSTAT寄存器用于选择I2C接口的工作模式,发出S信号、P信号,使能接收/发送功能,并标识各种状态,比如总线仲裁是否成功、作为从机时是否被寻址、是否接收到0地址、是否接收到ACK信号等。

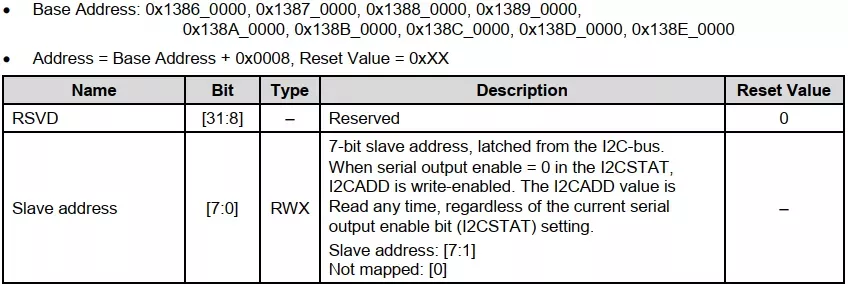

3 -- I2C数据发送/接收移位寄存器

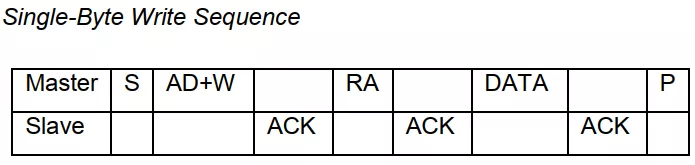

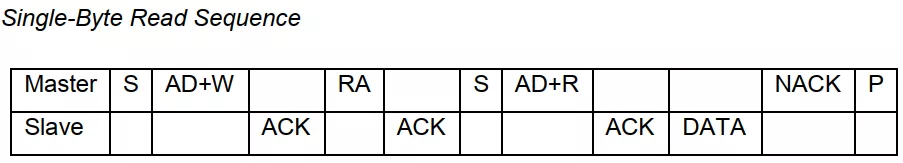

fs4412的i2c总线上挂载了mpu6050mpu6050每次读取或者要写入数据时,必须先告知从设备要操作的内部寄存器地址(RA),然后紧跟着读取或者写入数据(DATA),内部寄存器的配置和读取一次最多1个data,交互时序如下:

【注意】上述两个时序非常重要,下面我们编写基于linux的驱动编写i2c_msg还要再依赖他。

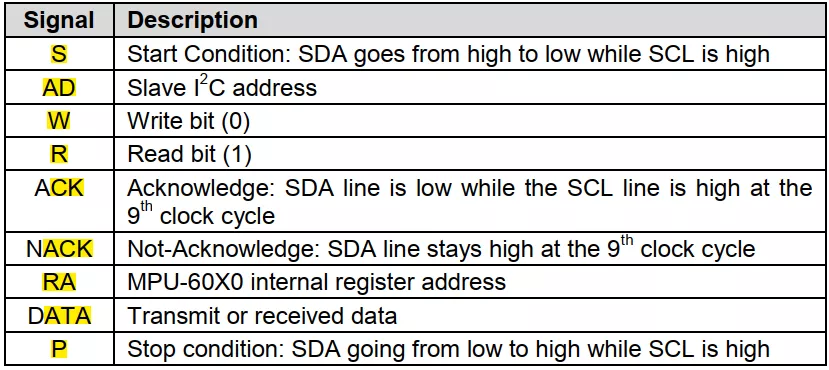

上述简化时序的术语解释如下

【寄存器使用规则】

下面先提前讲一下具体应用中如何启动和恢复IIC的传输 启动或恢复4412的I2C传输有以下两种方法。1) 当IICCON[4]即中断状态位为0时,通过写IICSTAT寄存器启动I2C操作。有以下两种情况。

- 1--在主机模式, 令IICSTAT[5:4]等于0b11,将发出S信号和IICDS寄存器的数据(寻址), 令IICSTAT[5:4]等于0b01,将发出P信号。

- 2--在从机模式,令IICSTAT[4]等于1将等待其他主机发出S信号及地址信息。

2)当IICCON[4]即中断状态为1时,表示I2C操作被暂停。在这期间设置好其他寄存器之后,向IICCON[4]写入0即可恢复I2C操作。所谓“设置其他寄存器”,有以下三种情况:

- 1--对于主机模式,可以按照上面1的方法写IICSTAT寄存器,恢复I2C操作后即可发出S信号和IICDS寄存器的值(寻址),或发出P信号。

- 2--对于发送器,可以将下一个要发送的数据写入IICDS寄存器中,恢复I2C操作后即可发出这个数据。

- 3--对于接收器,可以从IICDS寄存器读出接收到的数据。最后向IICCON[4]写入0的同时,设置IICCON[7]以决定是否在接收到下一个数据后是否发出ACK信号。

MPU6050

MPU-6000(6050)为全球首例整合性6轴运动处理组件,相较于多组件方案,免除了组合陀螺仪与加速器时间轴之差的问题,减少了大量的封装空间。当连接到三轴磁强计时,MPU-60X0提供完整的9轴运动融合输出到其主I2C或SPI端口(SPI仅在MPU-6000上可用)。

MPU-6000(6050)的角速度全格感测范围为±250、±500、±1000与±2000°/sec (dps),可准确追踪快速与慢速动作,并且,用户可程式控制的加速器全格感测范围为±2g、±4g±8g与±16g。

产品传输可透过最高至400kHz的IIC或最高达20MHz的SPI(MPU-6050没有SPI)。

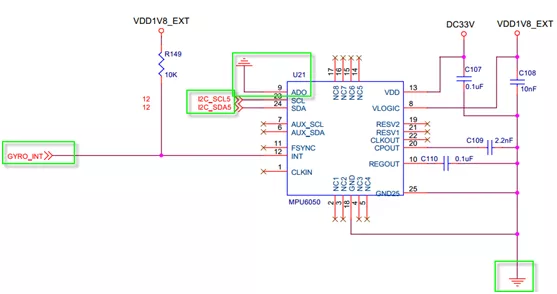

电路图

【MPU6050硬件电路图】(实际板子电路图不一定和下面一样,具体问题具体分析,本例参考exynos-fs4412开发板)

1 AD0接地的 值为 0

所以从设备地址为0x68;

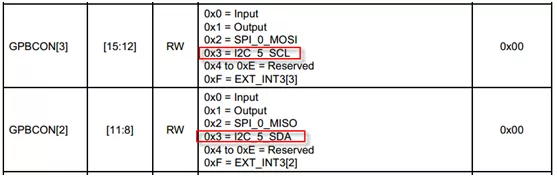

2 SCL、SDA连接的i2c_SCL5、i2c_SDA5

由此可得这两个信号线复用了GPIO的GPB的2、3引脚;

3 查阅exynos4412 datasheet 6.2.2 Part 1可得

所以设置GPIO 的 GPB 【15:8】= 0x33 即可。

MPU6050内部寄存器

mpu6050内部寄存器的使用,参考datasheet《MPU-6000 and MPU-6050 Register Map and Descriptions Revision 4.0 》。

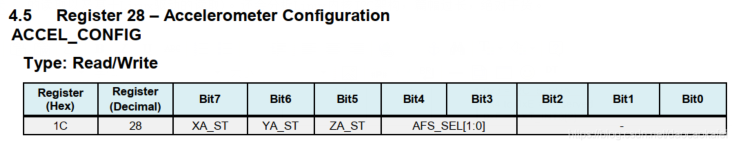

Mpu6050内部有100多个寄存器。比如:

这个寄存器是用来设置加速度属性的,当bit[4:3] 设置为0,表示3个轴的加速度量程最大为±2g。

mpu6050的内部寄存器非常多,并不需要每一个寄存器都需要搞懂,在如下代码实例中,我已经列举出常用的寄存器以及他们的典型值,其他的寄存器不再一一介绍。

下面是个IIC总线实例:用IIC总线实现CPU与MPU-6050的数据查询

具体代码如下:

- //****************************************

- // MPU6050常用内部地址,以下地址在mpu6050内部

- //****************************************

- #define SMPLRT_DIV 0x19 //陀螺仪采样率,典型值:0x07(125Hz)

- #define CONFIG 0x1A //低通滤波频率,典型值:0x06(5Hz)

- #define GYRO_CONFIG 0x1B //陀螺仪自检及测量范围,典型值:0x18(不自检,2000deg/s)

- #define ACCEL_CONFIG 0x1C //加速计自检、测量范围及高通滤波频率,典型值:0x01(不自检,2G,5Hz)

- #define ACCEL_XOUT_H 0x3B

- #define ACCEL_XOUT_L 0x3C

- #define ACCEL_YOUT_H 0x3D

- #define ACCEL_YOUT_L 0x3E

- #define ACCEL_ZOUT_H 0x3F

- #define ACCEL_ZOUT_L 0x40

- #define TEMP_OUT_H 0x41

- #define TEMP_OUT_L 0x42

- #define GYRO_XOUT_H 0x43

- #define GYRO_XOUT_L 0x44

- #define GYRO_YOUT_H 0x45

- #define GYRO_YOUT_L 0x46

- #define GYRO_ZOUT_H 0x47

- #define GYRO_ZOUT_L 0x48

- #define PWR_MGMT_1 0x6B //电源管理,典型值:0x00(正常启用)

- #define WHO_AM_I 0x75 //IIC地址寄存器(默认数值0x68,只读)

- #define SlaveAddress 0xD0 //IIC写入时的地址字节数据,+1为读取

- typedef struct {

- unsigned int CON;

- unsigned int DAT;

- unsigned int PUD;

- unsigned int DRV;

- unsigned int CONPDN;

- unsigned int PUDPDN;

- }gpb;

- #define GPB (* (volatile gpb *)0x11400040)

- typedef struct {

- unsigned int I2CCON;

- unsigned int I2CSTAT;

- unsigned int I2CADD;

- unsigned int I2CDS;

- unsigned int I2CLC;

- }i2c5;

- #define I2C5 (* (volatile i2c5 *)0x138B0000 )

- void mydelay_ms(int time)

- {

- int i, j;

- while(time--)

- {

- for (i = 0; i < 5; i++)

- for (j = 0; j < 514; j++);

- }

- }

- /**********************************************************************

- * @brief iic read a byte program body

- * @param[in] slave_addr, addr, &data

- * @return None

- **********************************************************************/

- void iic_read(unsigned char slave_addr, unsigned char addr, unsigned char *data)

- {

- /*根据mpu6050的datasheet,要读取数据必须先执行写操作:写入一个从设备地址,

- 然后执行读操作,才能读取到该内部寄存器的内容*/

- I2C5.I2CDS = slave_addr; //将从机地址写入I2CDS寄存器中

- I2C5.I2CCON = (1 << 7)|(1 << 6)|(1 << 5); //设置时钟并使能中断

- I2C5.I2CSTAT = 0xf0; //[7:6]设置为0b11,主机发送模式;

- //往[5:4]位写0b11,即产生启动信号,发出IICDS寄存器中的地址

- while(!(I2C5.I2CCON & (1 << 4))); // 等待传输结束,传输结束后,I2CCON [4]位为1,标识有中断发生;

- // 此位为1时,SCL线被拉低,此时I2C传输停止;

- I2C5.I2CDS = addr; //写命令值

- I2C5.I2CCON = I2C5.I2CCON & (~(1 << 4));// I2CCON [4]位清0,继续传输

- while(!(I2C5.I2CCON & (1 << 4)));// 等待传输结束

- I2C5.I2CSTAT = 0xD0; // I2CSTAT[5:4]位写0b01,发出停止信号

- I2C5.I2CDS = slave_addr | 1; //表示要读出数据

- I2C5.I2CCON = (1 << 7)|(1 << 6) |(1 << 5) ; //设置时钟并使能中断

- I2C5.I2CSTAT = 0xb0;//[7:6]位0b10,主机接收模式;

- //往[5:4]位写0b11,即产生启动信号,发出IICDS寄存器中的地址

- // I2C5.I2CCON = I2C5.I2CCON & (~(1 << 4)); 如果强行关闭,将读取不到数据

- while(!(I2C5.I2CCON & (1 << 4)));//等待传输结束,接收数据

- I2C5.I2CCON &= ~((1<<7)|(1 << 4));/* Resume the operation & no ack*/

- // I2CCON [4]位清0,继续传输,接收数据,

- // 主机接收器接收到最后一字节数据后,不发出应答信号 no ack

- // 从机发送器释放SDA线,以允许主机发出P信号,停止传输;

- while(!(I2C5.I2CCON & (1 << 4)));// 等待传输结束

- I2C5.I2CSTAT = 0x90;

- *data = I2C5.I2CDS;

- I2C5.I2CCON &= ~(1<<4); /*clean interrupt pending bit */

- mydelay_ms(10);

- *data = I2C5.I2CDS;

- }

- /**************************************************************

- * @brief iic write a byte program body

- * @param[in] slave_addr, addr, data

- * @return None

- *************************************************************/

- void iic_write (unsigned char slave_addr, unsigned char addr, unsigned char data)

- {

- I2C5.I2CDS = slave_addr;

- I2C5.I2CCON = (1 << 7)|(1 << 6)|(1 << 5) ;

- I2C5.I2CSTAT = 0xf0;

- while(!(I2C5.I2CCON & (1 << 4)));

- I2C5.I2CDS = addr;

- I2C5.I2CCON = I2C5.I2CCON & (~(1 << 4));

- while(!(I2C5.I2CCON & (1 << 4)));

- I2C5.I2CDS = data;

- I2C5.I2CCON = I2C5.I2CCON & (~(1 << 4));

- while(!(I2C5.I2CCON & (1 << 4)));

- I2C5.I2CSTAT = 0xd0;

- I2C5.I2CCON = I2C5.I2CCON & (~(1 << 4));

- mydelay_ms(10);

- }

- void MPU6050_Init ()

- {

- iic_write(SlaveAddress, PWR_MGMT_1, 0x00);

- iic_write(SlaveAddress, SMPLRT_DIV, 0x07);

- iic_write(SlaveAddress, CONFIG, 0x06);

- iic_write(SlaveAddress, GYRO_CONFIG, 0x18);

- iic_write(SlaveAddress, ACCEL_CONFIG, 0x01);

- }

- /*读取mpu6050某个内部寄存器的内容*/

- int get_data(unsigned char addr)

- {

- char data_h, data_l;

- iic_read(SlaveAddress, addr, &data_h);

- iic_read(SlaveAddress, addr+1, &data_l);

- return (data_h<<8)|data_l;

- }

- /*

- * 裸机代码,不同于LINUX 应用层, 一定加循环控制

- */

- int main(void)

- {

- int data;

- unsigned char zvalue;

- GPB.CON = (GPB.CON & ~(0xff<<8)) | 0x33<<8; // GPBCON[3], I2C_5_SCL GPBCON[2], I2C_5_SDAmydelay_ms(100);

- uart_init();

- /*---------------------------------------------------------------*/

- I2C5.I2CSTAT = 0xD0;

- I2C5.I2CCON &= ~(1<<4); /*clean interrupt pending bit */

- /*--------------------------------------------------------------*/

- mydelay_ms(100);

- MPU6050_Init();

- mydelay_ms(100);

- printf("\n********** I2C test!! ***********\n");

- while(1)

- {

- data = get_data(GYRO_ZOUT_H);

- printf(" GYRO --> Z <---:Hex: %x", data);

- data = get_data(GYRO_XOUT_H);

- printf(" GYRO --> X <---:Hex: %x", data);

- printf("\n");

- mydelay_ms(1000);

- }

- return 0;

- }

实验结果如下:

- ********** I2C test!! ***********

- GYRO --> Z <---:Hex: 1c GYRO --> X <---:Hex: feda

- GYRO --> Z <---:Hex: fefc GYRO --> X <---:Hex: fed6

- GYRO --> Z <---:Hex: fefe GYRO --> X <---:Hex: fed6

- GYRO --> Z <---:Hex: fefe GYRO --> X <---:Hex: fedc

- GYRO --> Z <---:Hex: fefe GYRO --> X <---:Hex: feda

- GYRO --> Z <---:Hex: fefc GYRO --> X <---:Hex: fed6

- GYRO --> Z <---:Hex: fefe GYRO --> X <---:Hex: feda

- GYRO --> Z <---:Hex: fcf2 GYRO --> X <---:Hex: 202

- GYRO --> Z <---:Hex: ec GYRO --> X <---:Hex: faa0

- GYRO --> Z <---:Hex: 4c GYRO --> X <---:Hex: e

- GYRO --> Z <---:Hex: fe GYRO --> X <---:Hex: fed8

- GYRO --> Z <---:Hex: 0 GYRO --> X <---:Hex: fede

- GYRO --> Z <---:Hex: 0 GYRO --> X <---:Hex: feda

读写操作代码解析:

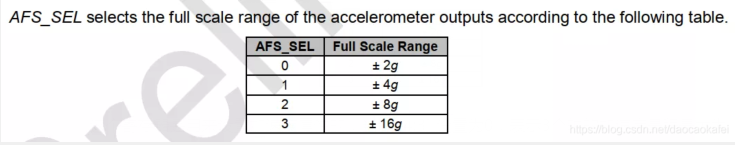

写入一个数据流程:

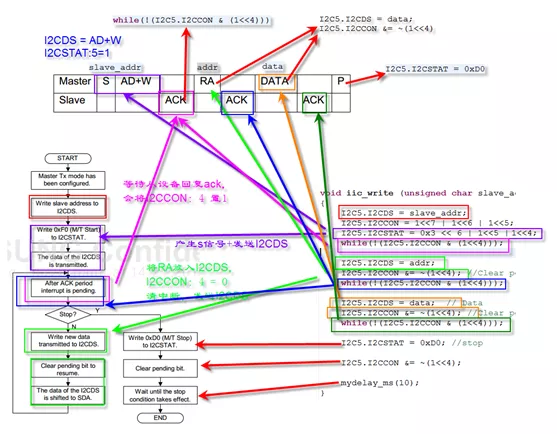

读数据流程:

上图阅读注意点:

- 从设备地址是在用的时候应该左移一位|读写位,比如写reg=0x68<1|0,即0xD0;

- 主设备发出S信号,需要将I2CSTATn 的bite:5设置为1;

- 主设备发出p信号,需要将I2CSTATn 的bite:5设置为0;

- 主机发送数据需要将寄存器I2CCONn的bit:4置0,to reume the operation;

- 主机等待从设备发送的ack或者data,需要轮训判断I2CCONn的bit:4是否置1;

- 代码的理解除了结合功能流程图、时序图、源代码还要结合寄存器说明;

- 代码的编写顺序必须严格按照时序和模块流程图执行;

- 时序中的每一个数据信号(包括ack、data、reg)的产生或者发送对应的代码都用箭头以及相同的颜色框处;

- 对1于read操作,NACK的回复需要在接收最后一个data之前设置I2CCONn :7位为0,这样在收到从设备的data后,才会将SDA拉低。