初创公司 Redwood EDA 经常与很多热情饱满的大学生、开源的开发者进行合作。

最近,超大规模集成电路系统设计的 Kunal Ghosh 举办了我们的第三次「30小时内为您服务的微处理器」(MYTH) 研讨会,参与者在那里学习 RISC-V 并构建他们自己的 RISC-V CPU 核心(通常在一两个学期内完成)。

除了面向研究生和专业人士,举办这个 Workshop 的目的之一是让学生在接受教育之前有机会学习逻辑设计。

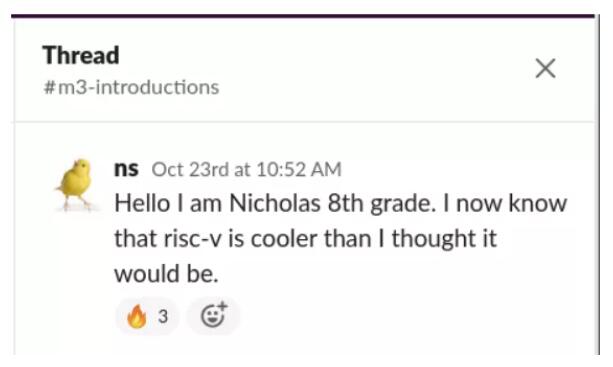

虽然8年级的尼古拉斯今年只有13岁,但他的确在5天的时间里完成了自己的一个RISC-V CPU。

不可否认,对尼古拉斯来说,这个 Workshop 是一个延伸,虽然对他来说没有达到30小时的要求。

在Workshop结束时,他已经完成了一半多一点:他学习了 RISC-V ISA 和编译工具; 发展了电路设计技能; 创造了一个流水线计算器电路; 他的第一个 RISC-V CPU 显示出了生命迹象。这是一个巨大的成功!

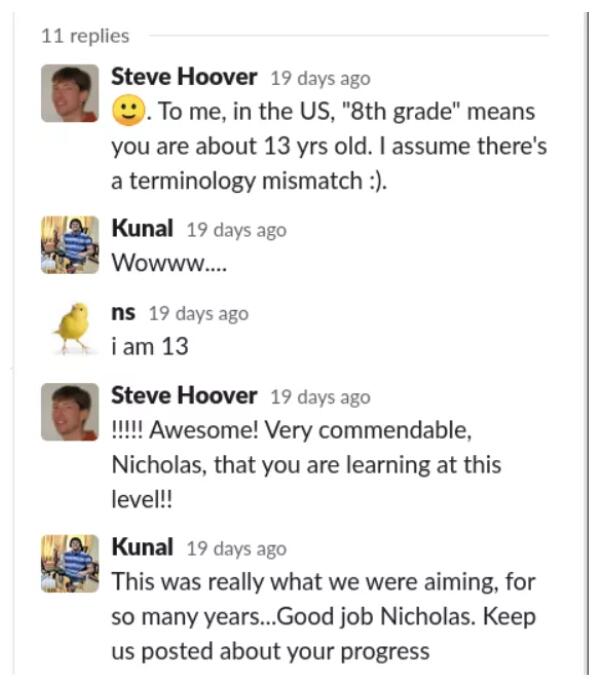

但是尼古拉斯在Workshop里连续工作了五天之后,仍然有毅力完成他的项目。

通常,当Workshop结束时,组织者们会关闭它,停止工作,但是他们同意给予一些特殊待遇,让尼古拉斯开学后在晚上继续来这里工作,进行他额外的学习。

这个研讨会总共有5天的课程,考虑到他的热情,估计 Nicholas 至少能够读完第四天的内容。

第五天,对他来说就有点过分了。第五天是真正看到学生如何吸收他们在第1-4天所教授的东西。在第5天,学生被要求Pipeline他们的 CPU,处理各种管道危险。这对一个13岁的孩子来说有点过分了,对吧?

但他竟然惊人的完成了!

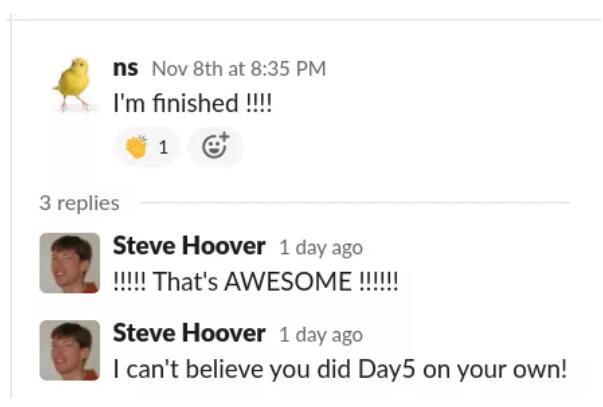

回顾他的工作,并与尼古拉斯讨论了它,组织者很高兴地说,尼古拉斯确实已经成功地完成了他的5阶段流水线 RISC-V CPU 核心,并将很快获得他的证书!

当组织人员问到他的经历时,他回答说“我非常喜欢这个挑战,它让我对 RISC-V 和数字设计感到兴奋。”他还对希瓦姆 · 波特达尔和 MYTH 的其他工作人员表示感谢。

什么是RISC-V?

RISC-V(发音为「risk-five」)是一个基于精简指令集(RISC)原则的开源指令集架构(ISA),可以简单解释为开源软件运动相对应的一种「开源硬件」。该项目2010年始于加州大学伯克利分校,但许多贡献者是该大学以外的志愿者和行业工作者。

与大多数指令集相比,RISC-V指令集可以自由地用于任何目的,允许任何人设计、制造和销售RISC-V芯片和软件而不必支付给任何公司专利费。

RISC-V指令集的设计考虑了小型、快速、低功耗的现实情况,但并没有对特定的微架构做过度的设计。

RISC-V的贡献者们旨在提供数种可以在BSD许可证之下自由使用的CPU设计。该许可证允许像是RISC-V芯片设计等派生作品可以像RISC-V本身一样是公开且自由发行,也可以是闭源或者是专有财产。

相比而言,ARM 和 MIPS 等商业芯片供应商会对使用其专利者收取高额的许可费用。

这些公司也会要求在接收其描述设计优点的文件和指令集前,还需要签署保密协议。许多设计优点为完全专有,从来不会披露给客户。这种保密制度阻碍了公共教育用途和安全审核,以及开发公共、低成本的自由及开放源代码软件编译器和操作系统。

开发一个CPU需要多种专业的设计知识,包括电子逻辑、编译器和操作系统,这种资源在专业工程团队之外很难见到。所以现代且高质量的通用计算机指令集近年来除了学术环境以外并没有在任何地方被广泛使用,甚至没有被阐述。

正因如此,许多 RISC-V 贡献者将此视为整个社区付出的成果,而这也是 RISC-V 有很多任务程上的应用的一项原因。

RISC-V的贡献者们还有大量研究和用户经验来验证他们在硅片和仿真中的设计。RISC-V指令集是从一系列的学术计算机设计项目直接发展而来的。它一开始的目的有一部分是为了帮助这些项目。