密码,无疑在系统安全和网络安全中扮演着至关重要的角色。

但是,随着具有强大密码破解能力的量子计算机不断取得实质性研究进展,目前广泛使用的RSA、ECC等公钥密码算法逐渐变得不再安全。

这对于现有的密码体系而言可以说是毁灭性的威胁。

为应对该类挑战,学术界和工业界早已开始着手研究能抵御量子计算攻击的后量子密码算法。

但问题在于,后量子密码算法的运算量通常非常巨大,想要真正应用和推广,就对专用后量子密码芯片提出了高要求:

必须要依靠高效的硬件架构,从而能以较低资源开销获得满足应用需求的执行速度。

现在,针对这一问题,清华大学魏少军、刘雷波教授团队提出了一种低计算复杂度数论转换与逆转换方法,以及一种高效的后量子密码硬件架构。

不仅能降低一类基于格的后量子密码算法的计算复杂度,还能在提高算法执行速度的同时减少了硬件资源开销。

实验结果表明,与最先进的方法相比,该设计在计算速度上快了2.5倍以上,同时面积延时积(ATP)减小了4.9倍。

这一成果刚刚登上了第22届密码硬件与嵌入式系统会议(CHES)。这是国际密码芯片和物理安全方向最重要的顶会之一。

后量子密码硬件加速技术

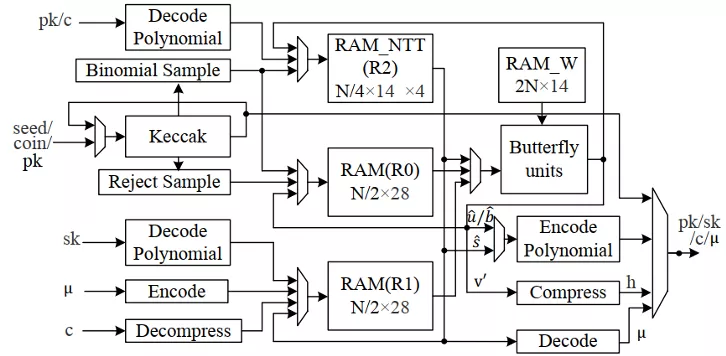

具体而言,这是一种应用于格密码的低计算复杂度数论转换方法及其硬件实现架构,可以同时优化算法执行时间和硬件资源开销。

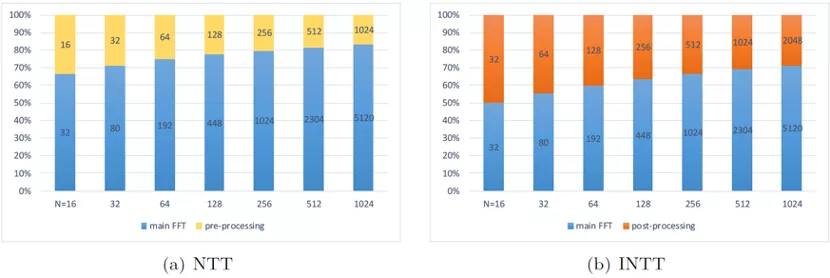

如下图所示,已有面向格密码的数论转换架构效率不高的症结在于其正变换和逆变换分别需要预处理与后处理,而预处理与后处理的计算量巨大,正是制约处理速度提升的瓶颈。

在清华的这项研究中,研究人员将预处理部分融合进时域分解快速傅里叶变换中,将后处理部分融合进频域分解快速傅里叶变换中,彻底去除了这两部分运算量。

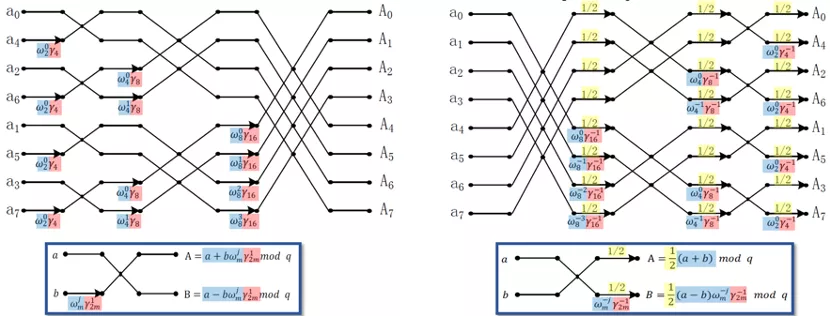

消除预处理和后处理后的低计算复杂度数论转换和逆数论转换,就像这样:

相比经典快速傅里叶变换,这个方法没有额外时间开销,硬件代价也非常小。

同时,研究人员还提出了一种能支持两种蝶形运算的紧凑型运算单元架构,针对NewHope算法的特定模数提出了一种无需执行乘法操作的恒定时间模约简方法,并据此设计了低复杂度数论转换硬件实现架构。

在同规模数论转换的硬件架构中达到执行速度最快,且减小面积延时积近3倍。

此外,这项研究还使用了双倍带宽匹配、时序隐藏等架构优化技术,进一步减小了执行NewHope算法的时钟周期数,设计了处理时间恒定的NewHope硬件架构。

实验结果表明,其计算速度相比已有最好结果快至少2.5倍,同时面积延时积减小了4.9倍。

关于作者

论文一作张能,目前正在清华大学微电子所攻读博士学位。

论文通讯作者是清华微电子所长聘教授刘雷波,主要合作者还有杨博翰、陈晨、尹首一等。

其实,在架构和芯片领域,清华魏少军、刘雷波教授的这支团队早已打响了名号。

△魏少军教授

过去10余年,魏少军、刘雷波教授团队在硬件安全与密码芯片领域取得了多项技术突破,关键技术在一系列国家重大工程中得到批量应用,曾获国家技术发明奖二等奖、教育部技术发明奖一等奖、电子学会技术发明奖一等奖、中国发明专利金奖、世界互联网大会15项世界互联网领先科技成果等多项重要科技奖励。

此前,该团队的《应用于事务内存的乐观并发控制算法的FPGA加速》还曾获MICRO最佳论文提名。这也是MICRO 52年历史上第二次有亚洲高校及机构获此殊荣。