了解更多数字化转型方案查看此链接:

https://www.dellemc-solution.com/home/index.html

高楼大厦、桥梁道路、种植

所需的土壤

均由一粒粒沙子构成

而驱动着互联网世界运转的

也是由沙子(硅)构成

自然界最普遍存在的元素——硅

同时支撑起了现实世界与虚拟世界

这不得不说是一种巧合

芯片,别称集成电路(缩写作IC)

代表了人类智慧的最高结晶

指甲盖大小的空间里

集成了数十亿甚至上百亿的晶体管

手机电脑里有芯片

冰箱空调洗衣机里有芯片

上天的卫星、入地的钻头也有芯片

是当今任何人都离不开的重要元件

我们都知道芯片是由沙子(硅)制成

但你知道从沙子到芯片的制作过程

需要经历几个步骤吗?

今天

我们一起走进芯片诞生记

☟☟☟

制成一颗芯片要几步?

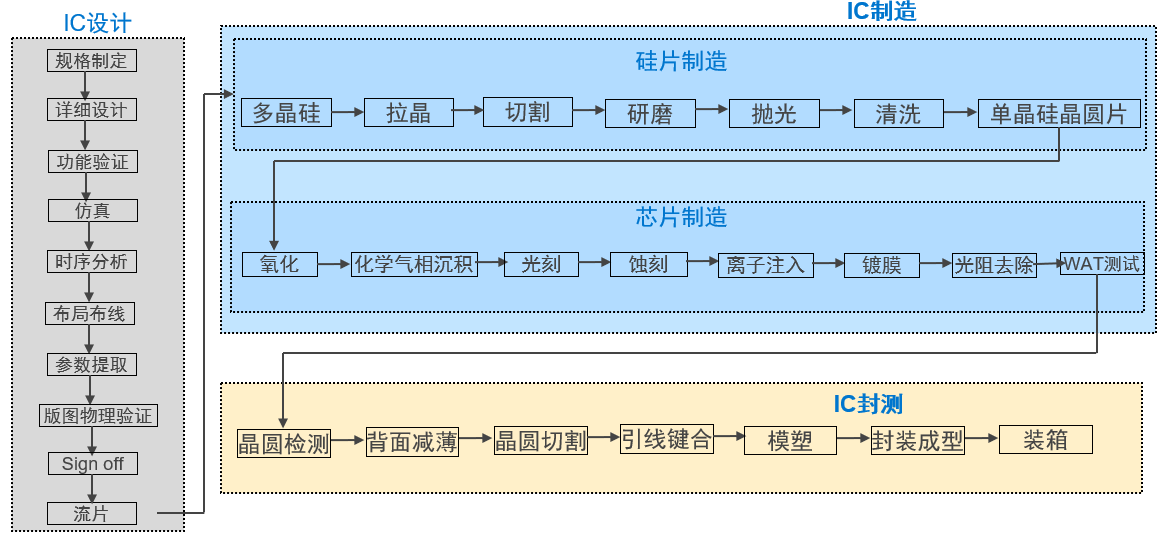

芯片制造,是一个“点沙成金”的过程,总体上分为三步,从上游的IC芯片设计,到中游的芯片制造,再到下游的封装测试,其间要经过数百道工艺的层层精细打磨,方可制成芯片成品。

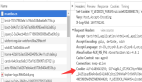

第一步:IC设计

在设计阶段,工程师用硬件描述语言(HDL)完成设计文件,随后由计算机自动完成电路逻辑的编译、化简、优化、布局、布线和仿真,直至对特定目标芯片的适配编译和逻辑映射等工作。芯片的用途、规格、特性、制成工艺,全部是在这个阶段完成的规范和设计。

相关数据显示,到2018年,中国IC设计企业已接近1700家。

第二步:IC制造

IC制造处于芯片工序的中游,这是个典型的重资产投入行业,涉及的关键制造设备有200多种,包括光刻机、蚀刻机、离子注入机、抛光机、清洗机等,每种设备都非常精密且成本昂贵。

芯片制造,从主要原材料石英砂(主成分是二氧化硅)开始。

▲英特尔制作的《从沙子到芯片》

石英砂经过高度熔炼、提纯,达到9个9的硅纯度,化学形态从多晶硅转化为三维空间规则有序排列、晶体结构非常稳定的单晶硅;

之后,通过拉伸工艺将单晶硅制成单晶硅锭,切割、研磨、镜面抛光之后制成厚度均匀、表面光滑、极度清洁的硅晶圆片;

硅晶圆片再经过光刻、蚀刻、离子注入、气相沉积等一系列工艺的“精雕细刻”,最终完成晶体管之间连接电路的构建并通过晶圆级测试。

这里不得不提的就是光刻机,光刻机作为制约芯片发展的关键要素,是核心技术中的核心。光刻通过光来制作图形,在硅片表面均匀涂胶,将掩膜版上的集成电路微型图形转印到光刻胶上。光刻直接决定了芯片的精度和质量,也是目前IC制造中难度最高的一环。

第三步:IC封测

封装和测试是芯片产业的下游,封装环节主要完成芯片的安放、固定、密封、保护,测试环节对芯片进行全面的测试,最终制成商用芯片产品。

“芯片之母”EDA

我们都知道,芯片制造从设计起步,是整个芯片制造流程中最难的步骤。芯片设计环节繁多、精细且复杂,其中,EDA工具发挥了极为重要作用。

EDA(Electronic Design Automation,电子设计自动化),是在电子CAD基础上发展起来的软件系统。随着芯片制成工艺和性能的提升,芯片设计的复杂度越来越高,肉眼很小的一块芯片,在显微镜则是由晶体管和电路组成的异常复杂的“立体高速公路”。

利用EDA工具,工程师将芯片的电路设计、性能分析、设计出IC版图的整个过程交由计算机自动处理完成,这极大提升了IC设计的效率和可操作性。EDA软件已成为IC设计的标配,被一些业内人士称为“芯片之母”。

而使用EDA软件工具进行IC设计,主要包含前端设计和后端设计两大阶段:

前端设计,侧重逻辑设计,根据芯片规格书完成芯片的逻辑和集成,使用仿真验证工具完成SOC的设计验证;

后端设计,侧重物理设计,根据前端设计产生的门级网表,通过EDA工具进行布局布线和物理验证。

当下,全球主要有Synopsys、Cadence、Mentor Graphics三大EDA软件厂商,可以为IC设计企业提供从前端到后端的整体设计流程服务,包含逻辑仿真、自动布局布线、物理设计、参数提取等各个设计环节的软件开发工具。

常言道,工欲善其事,必先利其器。IC设计的重要性不言而喻,EDA平台构建更是重中之重。构建符合IC设计企业级需求的EDA平台,除了选择合适的EDA软件工具,高性能可扩展的EDA IT基础设施平台亦是重要一环。

EDA平台存储需求:

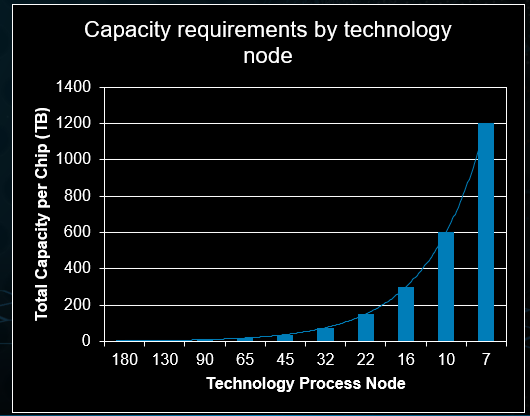

芯片制程工艺的每次提升,都会使IC设计环节产生的数据量大幅增加。据统计,2019年平均每设计一款芯片生成的数据量都要超过500TB,而大量的IC设计数据资料必须备份和长期保存。

在EDA前端设计阶段有大量的小文件生成,对随机IOPS要求很高,并要求目录深度;后端设计阶段,会生成很多大文件,对顺序IO性能和存储带宽有比较高的需求。

因此EDA数据存储系统,需要满足数以百计的Job同时访问,提供对应的高带宽性能与低访问延迟。

EDA平台计算需求:

由于EDA软件收费很高,更快的计算速度可以加速各个流程(设计、验证、模拟、测试),缩短IC设计所需计算时间——这意味着软件费用的大幅节省,同时有助于抢占市场先机,获取市场份额和高额利润。

因此,高计算速度也是EDA平台所追求的要件。

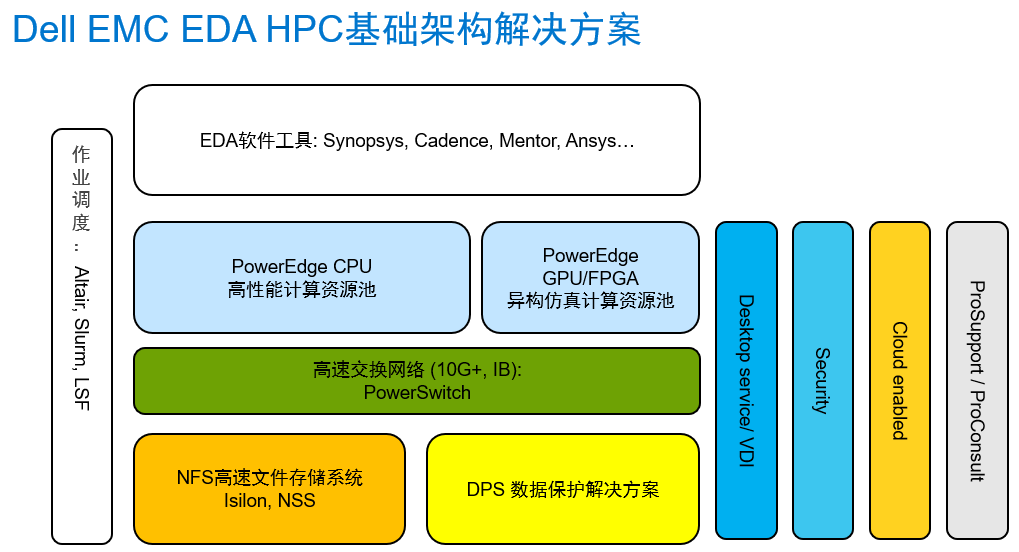

一体化EDA平台

戴尔易安信助力实现

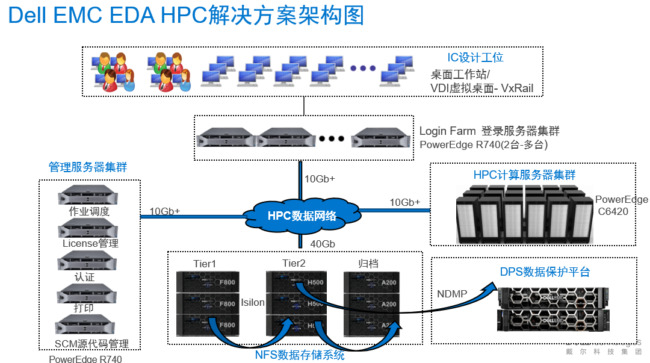

通过前文我们知道,在整个芯片设计过程中,EDA是重要一环。如果说设计人员决定了芯片设计过程的上限,那么EDA IT基础设施平台则决定了芯片设计过程的下限。因此IT基础设施平台对于芯片设计能否快速、顺利研发起到了重要作用。

在这方面,戴尔易安信提供了端到端的EDA HPC解决方案,包括CPU/GPU/FPGA计算、高性能NFS文件存储系统、高速交换网络、数据保护、HPC集群构建与作业调度在内的整体解决方案交付,可实现一体化构建EDA基础架构。

2U空间8颗处理器,专为速度而生

考虑到很多EDA软件工具按照CPU核心数计费,高主频处理器可以在提升计算性能的同时,降低软件费用的开支。

戴尔易安信PowerEdge C6420服务器,基于企业级高可用性与可扩展性而设计,搭载8颗英特尔®至强®处理器,2U空间内支持4个独立热插拔的双路服务器。

它内置DPAT性能优化技术(Dell Processor Acceleration Technology),DPAT能够精细到同一系统,不同CPU有各自的优化模板,可以使CPU核心在turboboost上获得更稳定的效能输出,针对高性能计算提供BIOS优化方案可以减少EDA各流程计算时间。

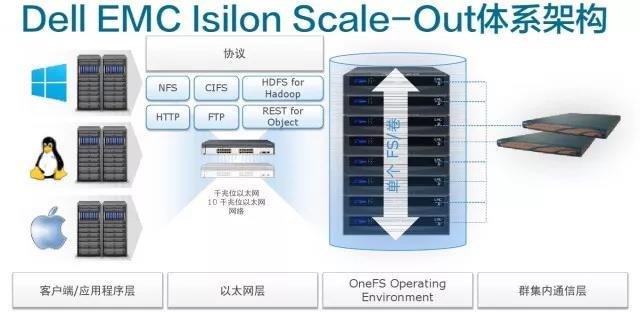

Isilon存储,实现性能无损的横向扩展

戴尔易安信Isilon采用分布式存储来替代传统中心存储,是一款能够实现上下平衡无瓶颈的分布式IT解决方案。

Isilon存储系统采用scale-out数据湖架构设计,可以轻松实现PB级容量扩展,它原生支持多种文件协议,能够满足开发和运维的整体性与敏捷度:NFS、SMB、HDFS、Object与Rest API。

基于Isilon存储,用户可以轻松实现存储的部署、管理、扩容,同步增加存储性能和容量,无须手动搬迁数据。此外,Isilon F800/F810全闪存单元,4U机箱内可以提供15GB/s的存储带宽和250K随机IOPS性能。

除了强劲的性能和容量支持,Isilon独有三大管理功能优势,可以优化EDA整体工作流程:

◇ 无需手动分拆EDA项目的目录 , 因为 Isilon没有100TB Volume的限制。

◇ 无需担忧特定EDA项目的负载, 因为Isilon真正分布式处理没有性能热点, 且可同时利用全部节点达到最佳性能。

◇ 无需手动搬移EDA项目的数据 , 因为Isilon可以自动平均数据,根据业务规模扩充即可。

*Isilon由英特尔®至强®处理器提供支持,该处理器采用软件定义的基础设施和敏捷云架构,为Isilon提供了卓越的性能和效率,可加速要求严苛的文件工作负载,使企业发挥数据资本的价值,加速业务的数字转型。

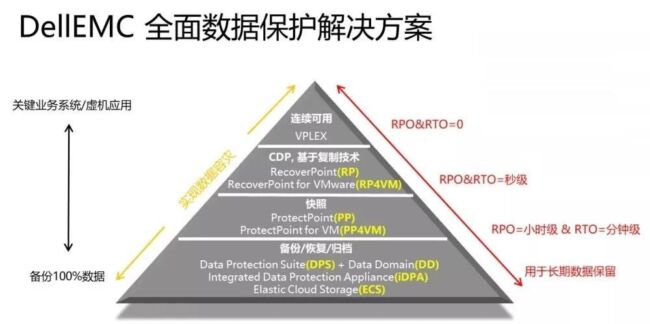

无缝数据保护,满足各种需要

戴尔易安信同样是数据备份保护领域的领导者,可提供全面的数据保护和高效的数据复制解决方案。使用NDMP协议,可以实现Isilon存储与戴尔易安信DPS备份设备之间的高速数据备份与恢复。

软硬结合、快速上线,加上模块化的设计及部署方案,戴尔易安信的一体化解决方案可以帮助EDA平台实现性能和容量的快速扩展,让芯片设计更加自动化、智能化。借助这些软硬件工具,希望我们的芯片设计师们可以更快速地设计出性能更好、质量更高、成本更低的芯片!

尊敬的读者

随着“Power”产品的不断推出涵盖从服务器到网络

从存储到数据保护的

戴尔科技“Power Family”

已经逐渐呈现在您的眼前藉此

我们隆重邀请您参加

2020年7月10日早9:00

新华网直播间重磅发布主题为

“奔涌之势 智造未来”

戴尔科技新一代

信息技术赋能新基建暨

2020新品发布会

届时同步通过多家主流媒体平台转播。戴尔科技集团将面向中国用户发布多款面向新一代信息技术的Power Family新产品家族及方案,并分享在中国市场各个领域的落地应用。

欢迎点击下方“阅读原文”

▼领取发布会入场券▼

相关内容推荐:新品:PowerScale里的DataIQ

相关产品:Dell EMC PowerScale F200 全闪存 NAS 节点