导读

据美国麻省理工学院(MIT)官网近日报道,该校研究人员用碳纳米管晶体管制作出一款新型微处理器。该微处理器被广泛认为是比传统硅处理器更快速、更绿色的替代品。

背景

晶体管,是人类现代历史中最伟大的发明之一。现代电子设备例如电脑、智能手机、智能硬件等,都离不开晶体管。在集成电路技术出现以后,大量的晶体管可被封装在一片指甲盖大小的芯片内。这种晶体管由源极、漏极和位于它们之间的栅极所组成,电流从源极流入漏极,栅极则起到控制电流开关的作用。

各种型号的晶体管(图片来源: 维基百科)

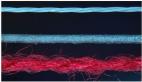

著名的摩尔定律指出:“当价格不变时,集成电路上可容纳的晶体管数目,约每隔18个月便会增加一倍,性能也将提升一倍。”正如摩尔定律所预测的,如今晶体管的尺寸在不断缩小,单颗芯片上集成的晶体管数量在不断增加,可以开展越来越复杂的运算。

摩尔定律-集成电路芯片上晶体管数量(1976-2016)(图片来源:维基百科)

但是近年来,摩尔定律正在面临严峻挑战。传统的晶体管主要都是由硅材料制成的。对于硅晶体管来说,7纳米堪称物理极限。一旦硅晶体管的尺寸低于这个数字,由于“量子隧道效应”,电子将不再受制于欧姆定律,穿越了本来无法穿越的势垒。这样会引起集成电路的漏电现象,让晶体管变得不再可靠。

为了解决上述问题,让摩尔定律继续焕发生机与活力,产业界与科学界的有识之士们开始积极寻找新材料,这些材料的目标就是取代硅,生产出尺寸更小、性能更佳、功耗更低的新一代晶体管。

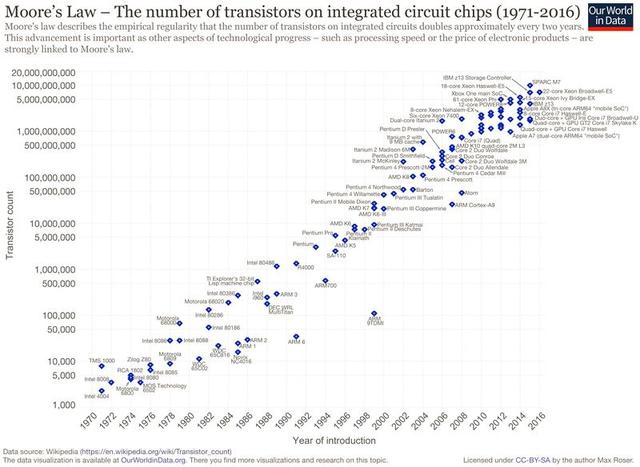

例如,笔者曾经介绍过美国劳伦斯伯克利国家实验室利用纳米碳管与二硫化钼研制出全球最小的晶体管,其晶体管制程仅为1纳米。

二硫化钼与1纳米碳纳米栅极组成的晶体管示意图 (来源: Sujay Desai/加州大学伯克利分校)

又例如,加拿大麦吉尔大学和蒙特利尔大学的研究表明,黑磷有望成为晶体管的一种非常好的候选材料。此外,其他的二维材料,例如石墨烯、六方氮化硼、二硒化钨等都可以用于打造新型晶体管。

其中,非常值得关注的材料之一就是碳纳米管(CNTs)。从形状上说,它主要是由呈六边形排列的碳原子构成数层到数十层的同轴圆管。碳纳米管作为一维纳米材料,重量轻,六边形结构连接完美,具有许多卓越的力学、电学和化学性能。

(图片来源:Michael Ströck / Wikimedia Commons)

制造碳纳米管场效应晶体管(CNFET)已成为打造新一代计算机的主要目标之一。研究表明,CNFETs 具有十倍于硅的能量效率,以及更快的运行速度。但是大规模生产时,这些晶体管通常会具有许多影响性能的缺陷,显得不切实际。

创新

近日,美国麻省理工学院(MIT)的研究人员在花费数年时间应对设计与制造方面的挑战之后,用碳纳米管晶体管制作出一款新型微处理器。该微处理器被广泛认为是比传统硅处理器更快速、更绿色的替代品。

由碳纳米管场效应晶体管制成的新型微处理器的显微图像。(图片来源:Felice Frankel)

8月28日,研究人员在《自然(Nature)》期刊上发表的论文中描述了这一微处理器。它采用传统的硅芯片制造工艺制造,代表了朝着制造更加实用的碳纳米管微处理器迈出了重要一步。

技术

MIT 的研究人员采用传统硅芯片铸造厂的工艺流程,发明了新技术,极大地限制了缺陷,并实现了 CNFETs 制造过程中的全功能控制。他们展示了一款具有14000个 CNFETs 的16位微处理器,它可以执行与商用微处理器相同的任务。《自然》期刊上的相关论文描述了微处理器的设计,包括70多页的详细制造方法。

由碳纳米管场效应晶体管制成的新型微处理器。(图片来源于研究人员)

该微处理器基于 RISC-V 开源芯片架构,该架构具有一组微处理器可以执行的指令。研究人员设计的微处理器可以准确地执行全部指令集,也执行了修改版的经典“Hello, World!(你好,世界!)”程序,打印出:“Hello, World! I am RV16XNano, made from CNTs.(你好,世界!我是 RV16XNano,由碳纳米管制成。)”。

电气工程与计算科学(EECS)系助理教授、微系统技术实验室成员、论文合著者 Max M. Shulaker 表示:“迄今为止,这是由新兴纳米技术制造出的最先进的芯片,它有望实现高性能且高能效的计算。硅具有局限性。所以,如果我们想要在计算领域继续取得进展,碳纳米管是最有希望克服这些局限的方法之一。研究论文彻底革新了我们用碳纳米管制造芯片的方式。”

除掉 CNFETs 的‘祸根’

这款微处理器是 Shulaker 及其他研究人员在6年前设计的一个迭代版本基础上开发的,当时的版本只有178个 CNFETs,并只能在单比特数据上运行。从那时起,Shulaker 和他在麻省理工学院的同事们就开始应对碳纳米管微处理器制造过程中的三个独特的挑战:材料缺陷、制造缺陷和功能问题。Gage Hills 负责大部分的处理器设计工作,而 Christian Lau 则负责大部分的制造工作。

Shulaker 表示,多年来,碳纳米管的固有缺陷一直是这个领域的“祸根”。理想情况下,CNFETs 需要半导体特性来打开或者关闭其导电性,分别与比特位是1或0相对应。但不可避免的是,一小部分的碳纳米管将会具有金属性,从而减缓或者阻止晶体管的开关。为了避免这些失败,先进的电路将需要纯度达99.999999%的碳纳米管,而这在现今几乎是不可能生产出来的。

研究人员提出了一项称为 DREAM(“designing resiliency against metallic CNTs”的缩写,即设计对抗金属性的碳纳米管)的技术。这项技术以一种方式放置金属性的 CNFETs,使之不会干扰计算。在这个过程中,他们将严格的纯度要求放宽了四个数量级,或者说1万倍,这意味着他们只需要纯度达99.99%的碳纳米管,而目前这是可以制备出来的。

基本上,设计电路需要一个由连接到晶体管上不同的逻辑门组成的库,而这些逻辑门可以组合到一起,就像将字母拼接成单词一样创造加法器和乘法器。研究人员发现,金属碳纳米管对于这些逻辑门的不同组合的影响是不同的。例如,逻辑门A中的单个金属碳纳米管,可能会破坏逻辑门A与逻辑门B之间的连接。但是逻辑门B中的几个金属碳纳米管却不会影响它们的连接。

在芯片设计中,有许多方法可以在电路上实现代码。研究人员进行了模拟,以找到所有不同的逻辑门组合,它们对于任何金属碳纳米管来说可能是“鲁棒性的”或者是“非鲁棒性的”。然后,他们定制了一个芯片设计程序,自动寻找最不可能受到金属碳纳米管影响的组合。当设计一个新型芯片时,程序将只利用“鲁棒”的组合,并忽略有漏洞的组合。

Shulaker 表示:“‘DREAM’这个双关语非常有意义,因为它是大家梦寐以求的解决方案。这个方法使得我们可以购买现成的碳纳米管,将它们放到晶圆上,像平常一样去构造我们的电路,不需要做其他任何特殊的事情。”

剥离与调优

CNFET 制造始于在溶液中将碳纳米管沉积到具有预先设计好的晶体管结构的晶圆上。然而,一些碳纳米管会不可避免地随机粘在一起,形成大束,就像意大利面串成小球一样,在芯片上形成了大颗粒污染物。

为了清除这种污染物,研究人员发明了 RINSE (removal of incubated nanotubes through selective exfoliation,用选择性剥离的方法去除孵化的纳米管)技术。晶圆会通过一种促进碳纳米管粘合的试剂进行预处理。然后,晶圆被涂上某种聚合物,并浸入一种特殊的溶剂中。这样一来可以冲走聚合物,而这些聚合物只能将带走大束的碳纳米管,而单个碳纳米管仍会粘附在晶圆上。与其他类似方法相比,该技术可使芯片上的颗粒密度降低约250倍。

最后,研究人员解决了 CNFET 常见的功能性问题。二进制计算需要两种类型的晶体管:“N”型晶体管,打开代表比特位为1,关闭代表比特位为0;“P”型晶体管则相反。传统意义上说,用碳纳米管制造这两种类型的晶体管是极具挑战性的任务,因为通常会产生性能各异的晶体管。为了解决这个问题,研究人员开发出一项称为 MIXED(metal interface engineering crossed with electrostatic doping,与静电掺杂交叉的金属界面工程)的技术,它能精确地调整晶体管的功能和优化。

在这项技术中,他们把某些金属(铂或钛)附着在每个晶体管上,这样就可以将晶体管固定为P或者N。然后,他们通过原子层沉积法将 CNFET 涂覆到某种氧化物化合物上,从而调整晶体管的特性,以满足特定应用的需求。例如,服务器通常需要运行速度快但耗电多的晶体管。从另一方面来说,可穿戴设备和医疗植入物可能需要速度较慢、功耗较低的晶体管。

未来

他们的主要目标是将该芯片推向现实世界。为实现该目的,研究人员现在已经开始通过支持这项研究的美国国防部高等研究计划局的一个项目,将他们的制造技术应用到一家硅芯片铸造厂中。虽然现在还没有人能断言,完全由碳纳米管制成的芯片何时将会上市。但 Shulaker 表示:“它可能在五年内得以实现。我们认为这不再是一个能否实现的问题,而只是何时实现的问题。