随着大数据和深度学习得到越来越多应用,对于底层硬件和芯片也提出了新的要求。与传统的处理器强调“处理能力”不同,大数据和深度学习应用强调的往往是“算力”以及“能效比”。由于大数据和深度学习应用算法中的特征提取和处理使用的都往往是实打实的计算,因此需要高算力的芯片以期在尽可能短的时间里完成计算。另一方面,能效比也是重要指标。能效比指的是完成计算所需要的能量,能效比越好则完成相同计算消耗的能量越小。

对于终端芯片, 越来越多的数据由于数据隐私、网络传输带宽和处理延迟的问题无法传到云端数据中心完成计算,这也就需要终端芯片能在终端完成计算;同时终端设备的电池容量往往有限,因此终端芯片在完成计算的同时不能消耗太大能量,也就是需要很好的能效比。对于云端数据中心的芯片,同样也需要很好的能效比,因为散热成本是数据中心的重要开销,因此需要芯片散热不能太大。

在大数据和深度学习应用中,数据间往往都是独立的,因此可以并行计算。传统的CPU并行计算能力有限,因此难以实现算力的需求。GPU虽然有很高的算力(10TOPS数量级)而且在数据中心已经得到了应用,但是其功耗也很大(几百瓦),而且其架构决定了它无法做到终端需要较低功耗(如100mW以下)的场景。同时,即使在数据中心领域,因为GPU设计的初衷是为了图像渲染而并非大数据运算,因此也存在很大的改善空间。

因此,我们看到了许多在AI芯片领域来自学术界和来自工业界的项目,试图挑战CPU和GPU。这些项目大体可以分为两类,一类是基于传统的数字处理器模型,但是在处理器架构上加以改良,以提高算力以及能效比;第二类则是另辟蹊径,使用了与传统处理器完全不一样的方法来执行计算,从而在一些领域中获得远高于传统处理器的性能。今天我们为大家带来的是第二类技术的总结,我们预期在第二类技术中会有一些能经历时间的考验,最终成为主流技术。

神经拟态计算

神经拟态技术(neuromorphic)事实上源远流长,上世纪八九十年代就由加州理工的电路大师Carver Mead提出。当时Mead教授注意到MOS器件中电荷流动的现象和人体神经元的放电现象有类似的地方,因此提出了用MOS管模拟神经元以组成神经网络进行计算,称之为“神经拟态”。

需要注意的是,神经拟态中的神经网络和现在深度学习算法中的神经网络略有不同。神经拟态电路中的神经网络是对于生物神经元和突触的高度模拟,包括了神经电位改变、发射脉冲等过程,该过程既可以用异步数字电路实现,又可以用混合信号电路实现;而深度学习中的神经网络是对于生物学中神经组织的抽象数学模拟,仅仅描绘了其电位变化的统计学特性而不会去具体描绘其充放电过程。然而,这个充放电过程却可能是为什么人脑如此节省能量的一个关键。人脑中复杂的神经网络能实现极其复杂的推理认知过程,然而其功耗却远小于一个GPU。

2017年5月美国橡树岭国家实验室发表了一篇重要的神经拟态研究综述,应当说目前人们对于神经拟态的研究还处于初步阶段,许多神经拟态架构的潜力还没有被人们发现,同时如何训练神经拟态电路也是一个重要的挑战。从现在的研究来看,人们发现神经拟态的神经元在不被激活的情况下功耗较低,因此可以实现较低的平均功耗,这是一个重要的优势。

举例来说,当我们部署一套摄像头加人工智能系统来识别是否有人进入摄像头视野时,往往很多时间并没有人出现在视野内。在这种情况下,使用传统的深度学习算法无论摄像头事业内情况如何都需要完成同样的计算,因此功耗保持恒定;而如果使用神经拟态芯片则神经元仅仅在有人进入摄像头事业时被激活,而在平时没有人进入视野时神经元处于待机状态功耗很低,因此其平均功耗可以远低于传统深度学习芯片。

换句话说,神经拟态电路的能效比可以远高于传统GPU/CPU芯片。除此之外,使用在终端的低功耗神经拟态芯片还能完成在线学习,而使用在终端的传统深度学习推理加速芯片往往没有在线学习的能力。这仅仅是神经拟态电路的一些好处,神经拟态电路的其他潜力还等待人们去挖掘。

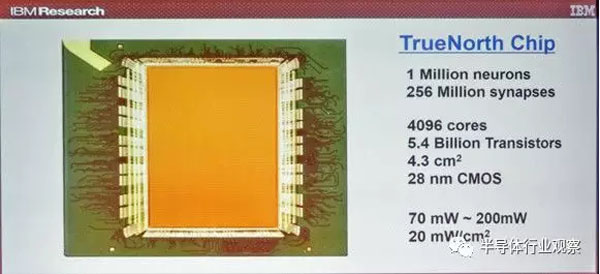

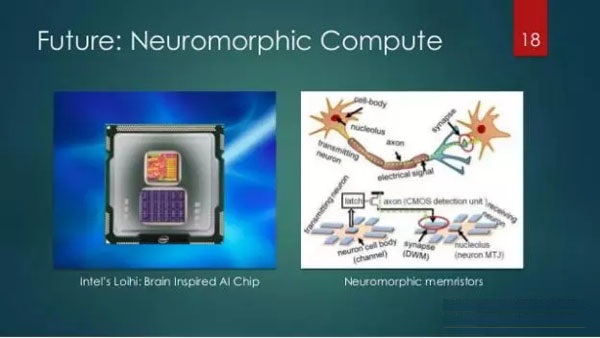

神经拟态电路芯片的潜力也是一些大公司开始布局的原因。IBM和Intel都推出了自己的神经拟态芯片(IBM和TrueNorth和Intel的Loihi),可以实现非常高的能效比。我们预期在未来看到更多的神经拟态电路芯片发布,能更多挖掘神经拟态的潜力。

光电计算

硅光子技术目前在数据中心和5G的高速数据传输中获得了越来越多的应用。除此之外,硅光子还可以用来以超低功耗直接加速深度学习计算。

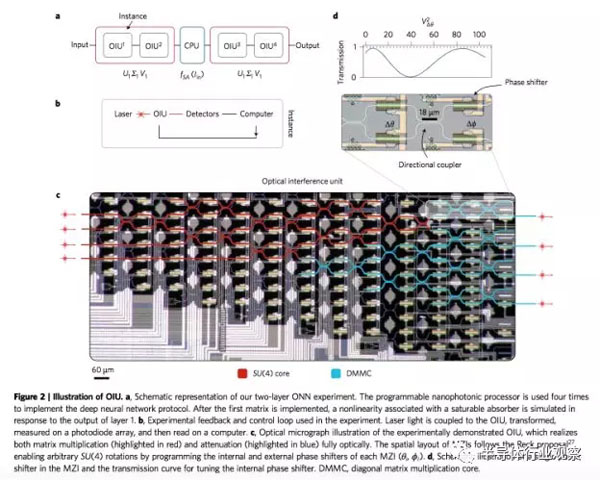

2017年,MIT的Marin Solijacic教授和其研究组在《自然·光子学》期刊上发表了一篇使用光学器件加速深度学习计算的论文。在深度学习中,绝大部分计算都可以归化为矩阵运算(这也是GPU用来做深度学习的原理),而实际应用中的矩阵都可以用SVD分解分解成几个特征矩阵的乘积。一旦使用SVD分解,则两个矩阵相乘可以使用光学器件(相移器,分光器,衰减器和马赫-曾德干涉仪)来实现。

更重要的是, 两个矩阵相乘的过程可以转化为两束光的干涉,因此深度学习的计算可以以光速完成而且理论功耗为零!该论文提出的设计就是首先把深度学习的两个输入调制到两束光上面,然后让两束光在光子芯片的器件上完成SVD分解和干涉相乘,***再把光信号转化为数字信号读出结果。***,这些光器件都可以集成到同一块硅光子芯片上,从而实现高性能光计算模组。

MIT的光模块用于计算深度学习

如前所述,一旦使用光干涉来实现深度学习计算,其计算速度就变成了光速,此外矩阵计算的功耗就变成了0,因此一旦能把光调制、光信号读出等光信号处理和接口模块的性能和功耗做好,整体系统的性能和能效比就能快速提升。 MIT的光计算团队孵化出了 初创公司Lightelligence,目前已经完成A轮融资,光电子用于深度学习的前景让我们共同拭目以待。

内存内计算

传统的AI加速器几乎都是基于冯诺伊曼架构,即内存访问和计算是分开的。冯诺伊曼架构的问题是内存访问,因为内存访问的功耗和延迟等问题都很难降下来,因此内存成为了处理器性能和功耗的瓶颈,也即所谓的“内存墙”。

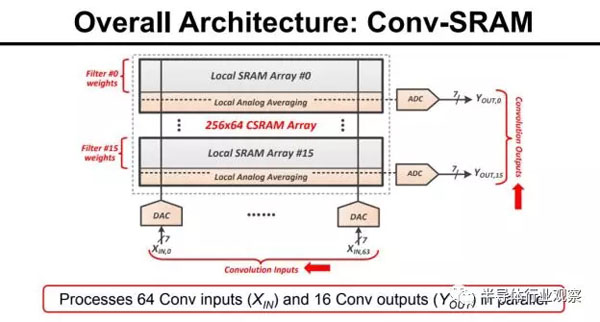

为了解决内存墙问题,不少学者提出了内存内计算的概念,这种概念在今年ISSCC上更是拥有了一个专门的session,可见学界对于这个方向还是很认可的。***的研究当属MIT Anantha Chandrakasan组。Anantha Chandrakasan在芯片领域可谓是鼎鼎大名,是数字电路经典教科书《Digital Integrated Circuits: A Design Perspective》的作者之一,同时也是低功耗数字电路设计、UWB系统等多个领域的先驱者,基本每年Chandrakasan组在ISSCC都会至少有一篇论文发表。今年ISSCC上Chandrakasan组发表的内存内计算论文针对的是权重压缩至1-bit的神经网络,当权重仅仅为1-bit的时候,卷积就可以约化成多个数据的平均,而求平均值使用经典的DAC中常用的电荷平均方法可以轻易实现。

因此,该内存中计算的论文实质上是在片上SRAM上接了一个类似DAC中电荷平均的电路,在内存内直接实现模拟计算来求卷积,从而不用再需要处理器和内存之间耗费大量时间和能量移动数据。计算后的结果使用ADC可以再次转化为数字信号。

相比传统的数字电路AI加速器,使用内存内计算加模拟计算的电路可以把能效比提高60倍以上,显示出了极大的潜力。当然,现在该电路还只能针对1-bit权重的网络,未来如何把内存内计算推广到更多应用场景,让我们拭目以待。

量子计算

量子计算是真正颠覆性的范式——当然前提是需要先能把量子计算机制造出来!

量子计算和经典计算***的不同在于,量子计算使用的是量子态。不同的量子态之间是可以互相线性叠加的,因此一个量子比特在测量前可以同时处于多个态的叠加中。而量子计算可以同时对多个叠加态进行操作,因此相当于做大量平行计算。

现在量子计算还处于非常早期研究阶段,目前只有少数量子算法可以利用量子特性实现指数级的加速,所谓“量子霸权”就是指在某个特定算法可以制造出相应的量子计算机使运行速度超过经典计算机。那么,量子计算如何加速人工智能呢?首先,目前正在积极研究量子版本的线性代数算法,有望实现指数级加速,而AI算法中许多计算的基础正是线性代数,因此一旦线性代数的量子版算法开发完成就可以大大加速人工智能计算。另外,以D-Wave为代表的量子退火算法有望能加速***化问题,而人工智能训练的一个最重要问题其实就是求***化解。因此,量子计算有望能加速人工智能。

谷歌和UCSB联合研发的20量子比特芯片

目前量子计算芯片有许多实现方式,包括工作在超低温下的离子阱和超导电路以及工作在常温的非线性光器件。应该说这些芯片目前还在很初期的阶段,虽然有些芯片已经能实现很多量子比特,但是量子退相干时间和量子门保真度仍然是性能的瓶颈。量子计算进入实用还有很长的路要走,但是一旦成功将会成为颠覆式的发展,这也是谷歌、IBM和微软等巨头都在积极布局量子计算的原因。

结语

本文介绍了一些全新的人工智能芯片技术,包括神经拟态、光电计算、内存内计算和量子计算。传统基于冯诺伊曼架构的人工智能加速器芯片存在内存墙等各种限制,我们有望看到这些新技术能在几年后正式登上舞台得到广泛应用。让我们拭目以待!