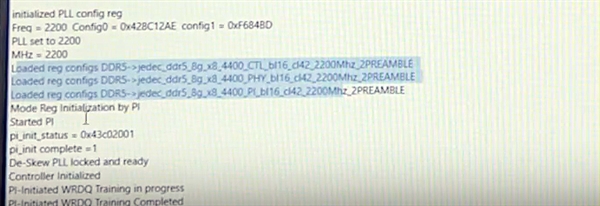

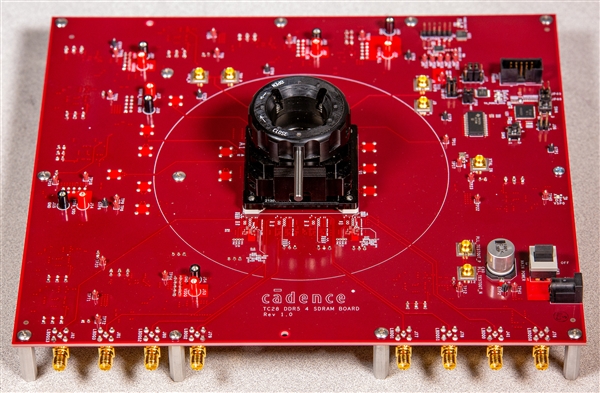

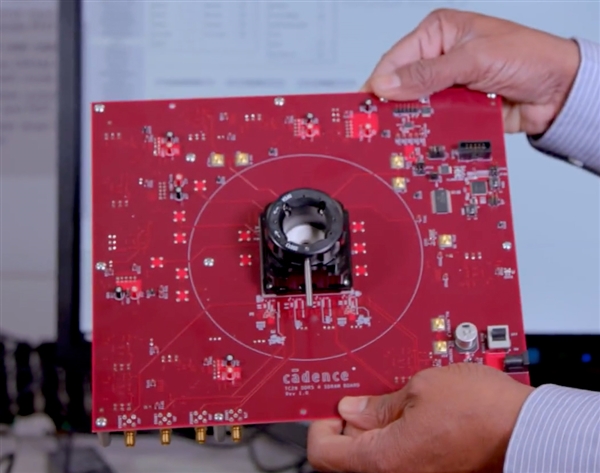

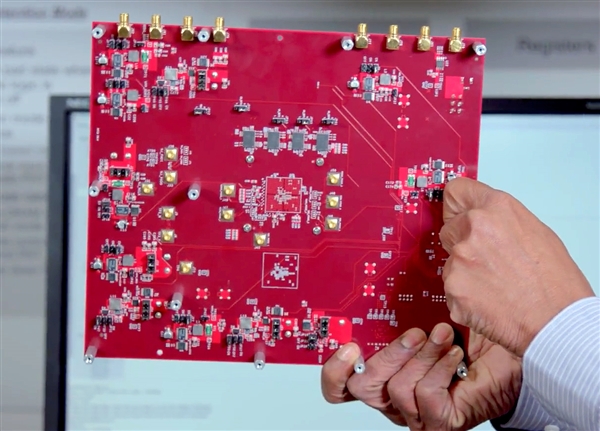

Cadence近日宣布了业内首个DDR5内存的IP接口芯片,包括控制器和PHY物理层,采用台积电7nm工艺制造,运行频率达4400MHz,美光也献上了自己的DDR5内存颗粒。

JEDEC组织目前正在制定DDR5内存的标准规范,预计今年夏天完成,所以目前进行的还都是一些基础性研究,DDR5内存条到底长什么样子还得等等。

Cadence DDR5内存控制器和物理层的数据率为4400MT/s,时序CL42,搭配美光8Gb DDR5内存颗粒原型,电压仅为1.1V(DDR4 1.2V),波动范围±0.033V。

有了这些基础,SoC芯片厂商就可以开始设计并集成DDR5内存子系统,为未来铺路。

正如DDR4内存频率从2133MHz一路走到3200MHz(JEDEC标准),4400MHz对于DDR5来说也只是起步,预计最终可以达到6400MHz左右。

除了频率,DDR5内存更看重的其实是大容量,允许加入内部ECC来制造16Gb、32Gb颗粒,单条容量也会大大提升。

DDR5内存仍将沿用288个针脚的布局,但具体设计肯定会和DDR4有所区别,并且有两个独立的32位IO通道,整体架构也会大有不同。

DDR5的其他改进还会有:更好的通道利用率、整合电压调节器、高端模组支持电源管理,等等。

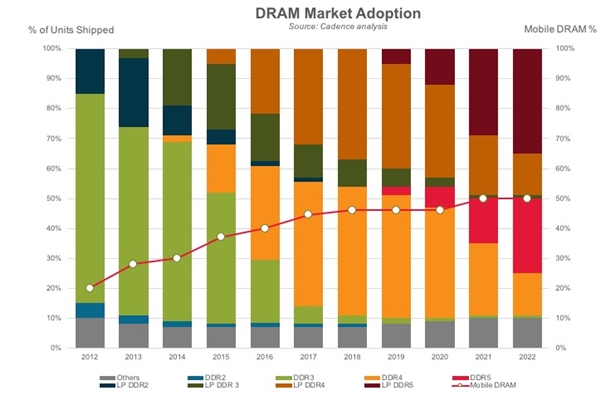

Cadence预计第一套DDR5内存系统会在2019年面世,然后迅速普及,2022年就能达到25%左右的渗透率。