本文讨论不同的存取技术对于DRAM在进行实体设计时所发生的改变,尤其是指由1电晶体+1电容器组成的储存单元——DRAM的最小记忆单位…

不同的存取技术对于动态随机存取存储器(DRAM)在进行实体设计时将发生什么改变?当动态随机存取存储器(DRAM)中的储存单元(storage cell)加上控制端点以及数据端点后,就被称为1T1C DRAM单元;其中,控制端点也就是字组线(WL),用于传递位址讯号,数据端点也就是位元线(BL),用于传递数据值。

阵列结构的差异

长期以来,对于DRAM单元阵列之中的位元线是使用差动对(differential pair)的样式来配置,于是位元线就被区分成“+BL”以及“-BL”;本文将这样的阵列结构命名为差动式储存阵列(Differential Storage Array),包含这种阵列结构的DRAM芯片就名为差动式DRAM芯片。相对于差动式储存阵列,新的存取技术可使用单端的样式来配置,于是位元线就是“BL”;本文将这样的阵列结构命名为单端式储存阵列,包含这种阵列结构的DRAM芯片就名为单端式DRAM芯片。

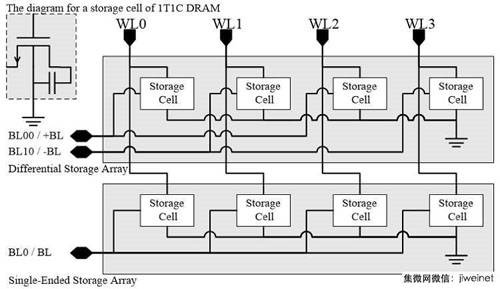

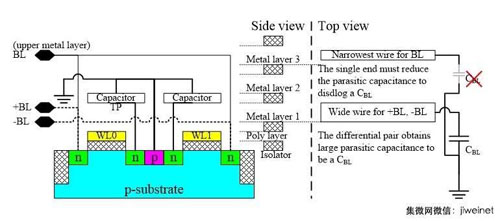

在图1左上方呈现储存单元的电路图,这就是1T1C DRAM芯片的记忆单位。在图1中,为了清楚比较差动式储存阵列与单端式储存阵列之间的差异,特别将上半部绘制成差动式储存阵列,又将下半部绘制成单端式储存阵列。这样本是将位址空间设定为4,其中,连接定址电路的导线即是WL0至WL3。连接数据传输电路的导线对于差动式储存阵列的设计是BL00 (+BL)以及BL10 (-BL),它的数据宽度是2,并且必为偶数,但是单端式储存阵列就止于BL0,它的数据宽度是1,可为奇数。差动式储存阵列有复杂的导线连接方式,并且必须交错连接位址线,这又被称为奇偶连线,像那BL00就是配合WL0以及WL2来存取数据。

从图 1可清楚看出单端式储存阵列相对于差动式储存阵列的优势,那就是简单俐落地连接全部的导线,这在布局的时候可减轻绕线的工作量以及简化储存单元的排列;在实体电路中可去除差动对的电压互相影响另一相对的储存单元,也就是在进行存取时会互相影响那些在储存单元之内的电压值,这原因归于电晶体的泄漏电流。

图1:差动式储存阵列与单端式储存阵列的差异

规格设计的差异

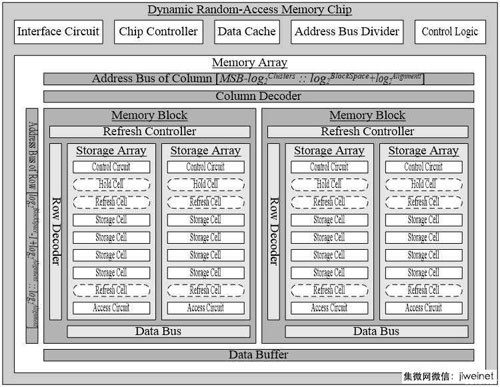

在规格设计上,DRAM芯片会配置许多储存阵列,本文将这些储存阵列所形成的布局区域命名为存储器阵列,并且这一存储器阵列又可分割出许多存储器区块,还可聚集这些存储器区块成一区块簇(Block Cluster)。关于本文所提出的DRAM芯片是以图2来呈现它的内部架构,这些存储器区块配置相同的定址空间,简称区块空间,这一区块空间包含多个与数据宽度相等的单端式储存阵列,或是包含多个与半数数据宽度相等的差动式储存阵列。在图中有标记保持单元(Hold Cell)以及更新单元(Refresh Cell),这需要分别配合主动保持(Active Hold)以及主动更新(Active Refresh)的功能。在存储器区块之内包含更新控制器以及列解码器即可经由平行技术来执行局部更新作业。

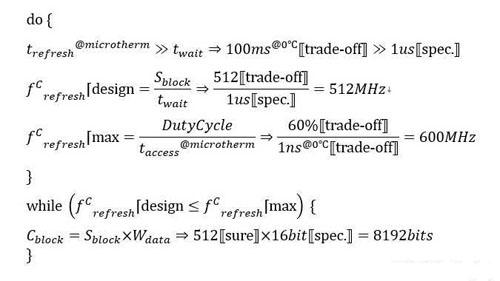

有许多因素可决定区块空间(Sblock),像是执行更新作业的时脉频率、等待更新作业完成的时间、执行更新作业的间隔时间以及执行存取作业的时间;以上这些因素分别简称为更新时脉频率(fCrefresh)、等待时间(t_wait)、更新时间(t_refresh)以及存取时间(t_access)。区块空间与数据宽度(W_data)的乘积就是存储器区块所含有的位元数,名为区块容量(C_block)。这些因素之间的关系可由以下的数学方程式来表达,并随附范例在后:

图2:DRAM芯片内部架构

实体结构的差异

在实体结构中,单一储存阵列上连接所有储存单元的单一位元线,该金属导线的长度以及寄生电容会限制区块空间的最大值,这要从储存阵列的布局以及储存单元的特性来分析这些因素。图3呈现有一实体结构来示意金属导线在晶粒上的布局,其中,侧视图呈现差动式储存阵列将那些与+BL以及-BL连接的金属导线放置在比较下面的金属层,像是第一金属层,在图中以粗点线示意;单端式储存阵列反而将那些与BL连接的金属导线放置在比较上面的金属层,像是第三金属层,在图中以细实线示意。顶视图呈现差动式储存阵列会加宽金属导线来增加寄生电容;单端式储存阵列反而要使用最小的线宽来去除寄生电容。

以下请对照图3,当WL0或WL1使得电晶体导通之后,与其连接的电容器就会向BL或+BL或-BL放电,位元线的电流经过一段金属导线之后连接至数据驱动器以及数据接收器。那些寄生在金属导线的全部电容在图中被标记为“C_BL”,这电容量也关联于实现回写功能的硬体电路;图中有一测试点(TP)用于探测储存单元的储存状态,它的电压值即是储存电压(V_storage)。当测试点的电荷逐渐移至金属导线之时,测试点的电压也会逐渐下降,除此之外,那些与位元线连接的电晶体皆有泄漏电流,甚至是数据驱动器的输出端,因此,那些移至金属导线的电荷又会被带走。如果提高C_BL的电容量就能够减缓电荷从金属导线被带走的速度,然而,金属导线需要从测试点取得更多的电荷来累积足够的电压值,如此才能判断数据值,此外会增加预充电的时间;这一现象会增加读取作业的时间以及回写作业的时间。如果C_BL的电容量能够趋近于零即可缩短预充电的时间,但是那些移至金属导线的电荷就会迅速流失,并且测试点的电压值也会迅速归零;这一现象如同发生了突波而导致数据接收器不能判断数据值,然而,这有可能经由增强数据接收器的整体效能而解决。这一寄生电容对于差动式储存阵列而言是需要足够大的电容量来判断数据值,对于单端式储存阵列反而期望得到最小的电容量,否则不止需要更长的回写时间来恢复储存状态,也有可能需要更大的电容量来维持正在读取之时的数据值,甚至无法判断数据值。

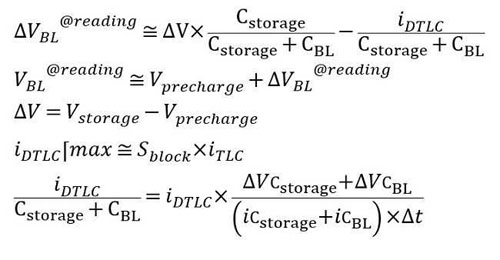

区块空间的最大值正比于数据接收器的整体效能,正比于那在储存单元内部的电容量(C_storage),反比于金属导线的寄生电容,反比于金属导线的总阻抗值,反比于电流路径之中的动态总泄漏电流(i_DTLC),这涵意即是每当有一储存阵列正在存取之时就会根据各储存单元的储存电压值而动态地变化。经由电容器的电荷分压定律而能算出正在读取数据之时那在位元线上的电压值,亦即“V_BL(@reading)”,数学方程式如后,其中,“V_BL(@reading)”是那在位元线上的差异电压值,“V_precharge”是预充电的电压值,这电压值在差动式储存阵列是1/2V_dd,在单端式储存阵列是0:

图3:内含2种储存单元的实体结构差异

储存电压的差异

在进入这段的主题之前要先清楚定义以下的名词:“电源电压(V_dd)”是位于储存单元之外的供应电压,也就是向着数字逻辑电路而供应正电压的电源;“储存电压(V_storage)”是位于储存单元之内用于接收电压值并且尽量维持其所对应的逻辑准位来提供读取期间的数据值;“鉴别电压(V_discerning)”是数据接收器在读取期间或更新期间能够对最微小的电压变化而鉴别数据值的极限值;“最小杂讯边界(V_margin〡MIN)”是数据接收器在读取期间或更新期间内受到各类杂讯的干扰时也能够鉴别数据值的最小边界电压值,这些杂讯包含电源杂讯以及切换杂讯;“最小差异电压(ΔV〡MIN))”等于鉴别电压加上最小杂讯边界,是在读取期间或更新期间能够在受到杂讯干扰之时也能被数据接收器鉴别数据值的最小储存电压,这电压也会影响更新时间的极限值。另外,“单元电压(V_cell)”是笔者发表有关SRAM的存取技术时所提出的一种供应电压,这用途不同于储存电压。

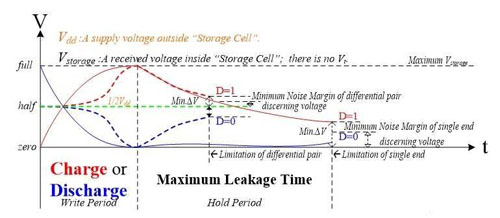

图4呈现差动式储存阵列以及单端式储存阵列的储存电压,并且突显在单一储存单元之中的差异。为了忽略不同的储存阵列在存取技术上的差异,所以这电压波形图所对应到的硬体电路就是单一储存单元。换言之,这是设定在相同的制程参数、电容量以及泄漏电流来比较关于储存电压的差异。

电晶体的闸极电压(V_t)会使得储存电压低于电源电压,如果逐渐增加电晶体的闸极电压则可使得储存电压逐渐趋近电源电压。差动式储存阵列为了去除闸极电压,于是在存取期间之内会令字组线的电压值至少到达电源电压加上闸极电压,使得最大的储存电压等于电源电压。单端式储存阵列除了可经由上述的增压方法来达到同样的效果之外,尚可经由多闸极电压的制程技术来使用高闸极电压的电晶体,如此还能减小泄漏电流。对于减小泄漏电流的电路也能使用三阱制程(triple-well process)来设计列解码器的输出驱动器,如此即可令字组线以负电压截止电晶体。

图4的电压波形图是呈现去除闸极电压的影响而形成的工作状态。在写入期间之内,差动式储存阵列的储存电压会先到达预充电的电压值,然后到达所被写入的电压值;然而,单端式储存阵列没有预充电的电压值。在保持期间之内,差动式储存阵列的储存电压会逐渐趋近半倍的电源电压值;然而,单端式储存阵列是逐渐趋近最小的电压值,亦即接地电压值。由此看出单端式储存阵列的更新时间大约是差动式储存阵列的二倍。

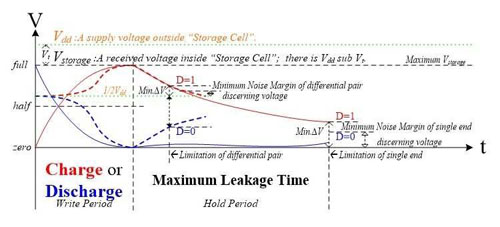

图5是为了突显差动式储存阵列与单端式储存阵列之间的效益差异,所以这电压波形图呈现加入闸极电压所形成的影响。在写入期间之内,最大的储存电压值低于电源电压值,这影响了差动式储存阵列的电压对称性。在保持期间之内,对于差动式储存阵列的储存电压,放电曲线比充电曲线更快到达半倍的电源电压值,使得更新时间被迫缩短。由此看出单端式储存阵列的更新时间超过差动式储存阵列的二倍。

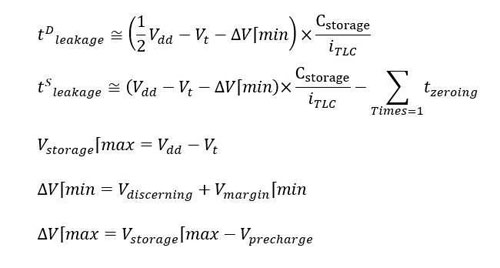

经由上述的分析而得知一些会影响时间的因素,其中,泄漏电流是主要因素,并且正比于工作温度。关于在差动式储存阵列内部单一单元的泄漏时间(tDleakage)以及在单端式储存阵列内部单一单元的泄漏时间(tSleakage)可由以下的数学方程式来表达,其中,“t_zeroing”代表单端式储存单元在每次对储存电压执行归零的时间,亦即启动主动保持功能的时间:

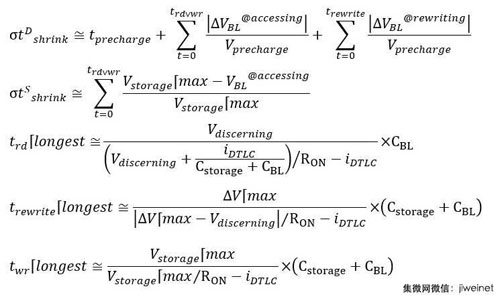

由于每当有一储存阵列正在存取之时就会影响内部各储存单元的更新时间,所以其余储存单元受到这一存取作业而被缩短了更新时间就名为收缩时间。差动式储存阵列的收缩时间(σtDshrink)以及单端式储存阵列的收缩时间(σtSshrink)可由以下的数学方程式来表达,其中,“t_precharge”代表预充电时间,“t_rdvwr”代表读取或写入时间,“t_rewrite”代表回写时间:

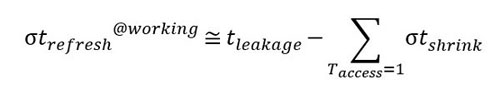

关于各种储存阵列在工作中的动态更新时间(σt_refresh@working)可由以下的数学方程式来表达,并且动态更新时间不同于设计上的更新时间,其中,“T_access”代表执行存取作业的次数:

图4:储存单元(不带Vt)的储存电压比较

图5:储存单元(带Vt)的储存电压比较

结论

差动式储存阵列的存取电路很容易经由习以为知的电路来实现,然而,单端式储存阵列的存取特性对于数据接收器的设计是一重大的考验,由此可推知1T1C DRAM单元在出现以来就是使用差动放大器来读取数据。本文对于DRAM存取技术的改变而形成了这种单端式储存阵列,乃是基于由三电晶体结合另一电阻器所组成的SRAM单元。简言之,静态减量技术成,动态存取特性同。在标准的CMOS制程技术下,当SRAM单元的电晶体数量减少至三颗的时候就少了些原有的特性,尤其是存取特性的迵异,并且类似于DRAM单元。