1. 冯·诺依曼结构

冯·诺依曼结构,又称为普林斯顿体系结构,是一种将程序指令存储器和数据存储器合并在一起的存储器结构。取指令和取操作数都在同一总线上,通过分时复用的方式进行;缺点是在高速运行时,不能达到同时取指令和取操作数,从而形成了传输过程的瓶颈。由于程序指令存储地址和数据存储地址指向同一个存储器的不同物理位置,因此程序指令和数据的宽度相同,如英特尔公司的8086中央处理器的程序指令和数据都是16位宽。

目前使用冯·诺依曼结构的CPU和微控制器有很多。其中包括英特尔公司的8086及其他CPU,TI的MSP430处理器,ARM公司的ARM7,MIPS公司的MIPS处理器。

2. 哈佛结构

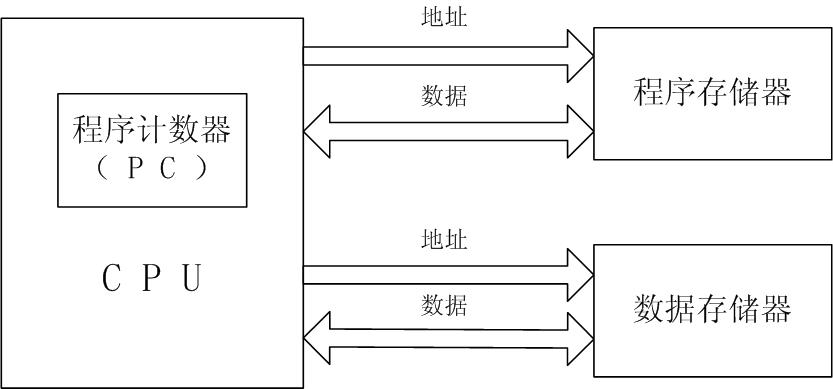

哈佛结构是一种将程序指令存储和数据存储分开的存储器结构,它的主要特点是将程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个独立的存储器,每个存储器独立编址、独立访问,目的是为了减轻程序运行时的访存瓶颈。

如图,哈佛结构的计算机由CPU、程序存储器和数据存储器组成,程序存储器和数据存储器采用不同的总线,从而提供了较大的存储器带宽,使数据的移动和交换更加方便,尤其提供了较高的数字信号处理性能。

目前使用哈佛结构的中央处理器和微控制器有很多,除了上面提到的Microchip公司的PIC系列芯片,还有摩托罗拉公司的MC68系列、Zilog公司的Z8系列、ATMEL公司的AVR系列和安谋公司的ARM9、ARM10和ARM11。

3. 总结

随着CPU设计的发展,流水线的增加,指令和数据的互斥读取影响CPU指令执行的scale程度。哈佛结构中数据存储器与程序代码存储器分开,各自有自己的数据总线与地址总线,取操作数与取指令能同时进行。但这是需要CPU提供大量的数据线,因而很少使用哈佛结构作为CPU外部构架来使用。对于CPU内部,通过使用不同的数据和指令cache,可以有效的提高指令执行的效率,因而目前大部分计算机体系都是在CPU内部的使用哈佛结构,在CPU外部使用冯·诺依曼结构。

原文链接:http://blog.csdn.net/skywalker_leo/article/details/7819463