对于HART协议来说,我们更多地是讨论它在通讯方面的应用。例如总线,现场仪表等硬件设计。另外在一些软件设计中,它也同样有着广阔的前景。现在我们就来研究一下在这些方面HART协议的一些工作原理吧。

一、HART协议简介

HART(Highway Addressable Remote Transducer),可寻址远程传感器高速通道的开放通讯协定,是美国Rosemen于1985年推出的一种用于现场智能仪表和控制室设备之间的通讯协定。

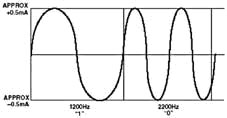

HART装置提供具有相对低的带宽,适度响应时间的通讯,经过10多年的发展,HART技能在国外已经十分成熟,并已成为全球智能仪表的工业标准。HART协议采纳基于Bell202标准的FSK频移键控信号,在低频的 4mA~20mA模拟信号上叠加幅度为0.5mA的音频数字信号进行双向数字通讯,数据传输率为1.2Mbps。由于FSK信号的平均值为0,不影响传送给节制体系模拟信号的大小,保证了与现有模拟体系的兼容性。

在HART协议通讯中,重要的变量和节制信息由4mA~20mA传送,在需要的情况下,另外的测量、历程参数、设备组态、校准、诊断信息通过HART协议访问。

HART通讯采纳的是半双工的通讯法子。HART协议参考 ISO/OSI(开放体系互连模型),采纳了它的简化三层模型构造,即第一层物理层,第二层数据链路层和第七层利用层。

第一层:物理层。规定了信号的传输法子、传输介质,为了实现模拟通讯和数字通讯同时进行而又互不干扰,HART协议采纳频移键控技能 FSK,即在4mA~20mA模拟信号上迭加一个频率信号,频率信号采纳 Be11202国际标准,数字信号的传送波特率设定为 1200bps,1200Hz代表逻辑“0",2200Hz代表逻辑“1",信号幅值0.5A,如图1所示。

通讯介质的选择视传输距离长短而定。通常采纳双绞同轴电缆作为传输介质时,最大传输距离可到达1500m。线路总阻抗应在230Ω~1100Ω。

第二层:数据链路层。规定了HART帧的格式,实现创建、保护、终结链路通讯功效。HART协议依据冗余检错码信息,采纳主动反复恳求发送机制,打消由于线路噪音或其他干扰引起的数据通讯出错,实现通讯数据无过错传送。

现场仪表要实行HART指令,操作数必需合乎指定的大小。每个独立的字符包括1个起始位、8个数据位、1个奇偶校验位和一个停滞位。由于数据的有无和长短并不恒定,所以HART数据的长度也是不一样的,最长的HART数据包括25个字节。

第三层:利用层。为HART命令集,用于实现 HART指令。命令分为三类,即通用命令、普通命令和专用命令。#p#

二、现场仪表HART协议远程通讯硬件设计

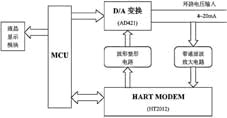

某现场仪表的HART协议部分重要完成数字信号到模拟电流信号的转换,并实现对重要变量和测量、历程参数、设备组态、校准及诊断信息的访问。图2是HART协议通讯模块构造设计框图。

HART通讯部分重要由D/A转换和Bell202 MODEM及其从属电路来实现。其中,D/A变换作用是直接将数字信号转换成4mA~20mA电流输出,以输出重要的变量。Bell202 MODEM及其从属电路的作用是对叠加在4mA~20mA环路上的信号进行带通滤波放大后,HART通讯单元如果检测到FSK频移键控信号,则由Bell202 MODEM将1200Hz的信号解调为“1",2200Hz信号解调为“0"的数字信号,通过串口通讯交MCU,MCU接受命令帧,作相应的数据处理。然后,MCU产生要发回的应答帧,应答帧的数字信号由MODEM调制成相应的1200Hz和2200Hz的FSK频移键控信号,波形整形后,经AD421叠加在环路上发出。

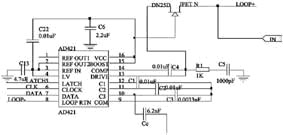

D/A变换器采纳AD421,它是美国ADI公司推出的一种单片高性能数模转换器,由环路供电,16位数字信号以串行法子输入,可以将数字信号直接转换成4mA~20mA电流输出。它提供了高精度、全集成、低功耗的解决规划,采纳16引脚DIP、TSSOP、SOIC封装,可实现低成本的远程智能工业节制。AD421包括串行输入16位 D/A(数字/电流 )转换,除自身用电外,还提供可选择的(5V,3.3 V或 3 V)稳压输出供变送器其他部分用电。

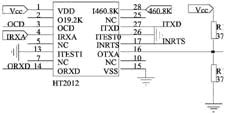

HART MODEM采纳 Smar公司的 HT2012,是符合Bell202标准的半双工调制解调器,实现HART协议规定的数字通讯的编码或译码。该芯片专为 HART仪器设计,片内集成了符合 BELL202标准的调制器、解调器、时钟及定时电路、检测节制电路。性价比较高,16脚 DIP和28脚PLCC封装,在+5V供电时工作电流80μA。HT2012与微节制器交换数字信号,同AD421作模拟信号接口。它一方面与MCU的异步串行通讯口进行串行通讯,一方面将输入的不归零的数字信号调制成FSK信号,再经AD421叠加在4mA~20mA的回路上输出,或者将回路信号经带通滤波、放大整形后取出FSK信号解调为数字信号,从而实现HART通讯。

对于HART MODEM所需要的输入时钟,采纳7.3728MHz的晶振通过两个计数器74LS161进行两次4分频,得到16分频的时钟。

由于HART数字通讯的要求,有0.5mA的正弦波电流信号叠加在4mA电流上,因此全部硬件电路必需保证在3.5mA以下还能正常工作,因此实现体系的低功耗设计非常重要。

图3和图4分别是采纳的AD421和HT2012的外围电路图。

#p#

#p#

三、通讯的软件设计

HART通讯程序也即为HART协议数据链路层和利用层的软件实现,是全部现场仪表软件设计的症结。

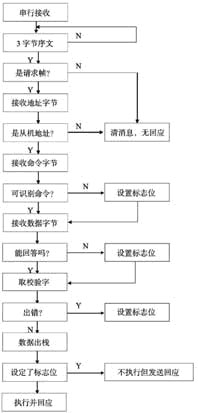

在HART通讯历程中,主机(上位机)发送命令帧,现场仪表通过串行口中止接受到命令帧后,由MCU作相应的数据处理,产生应答帧,由MCU触发发送中止,发出应答帧,从而完成一次命令交换。

首先在上电或者看门狗复位后,主程序要对通讯部分进行初始化,重要包括波特率设定、串口工作法子设定、清通讯缓冲区、开中止等。

在初始化完成之后通讯部分就一直处在准备接受状态下,一旦上位机有命令发来,HT2012的载波检测口OCD变为低电平,触发中止,启动接受,程序就进入接受部分。然后完成主机命令的解释并依据命令去实行相应的操作,最后按必然的格式生成应答帧并送入通讯缓冲区,启动发送,完成后关闭SCI。

图5是串行接受恳求帧、回复应答帧程序的流程图。

在发送应答帧之后,再次进入期待状态,期待下一条主机命令。

四、结语

实践证明,上述法子具有构造简略、工作可靠的特点,完全符合HART协议,具有较好的通用性。

由于HART众多不容置疑的长处,使得它成为全球利用最广的现场通讯协定,已成为工业上适用的标准。因此在今后很长一段时代内,HART协议在国内仍然具有十分辽阔的市场。