GPT-4(o)免费试用体验,看看它的设计方案能力—关于ROCE网卡方案

OpenAI 新发布了最新多模态AI 模型GPT-4o。这个模型的“4o”中的“o”代表“omni”,意为“全能的”。

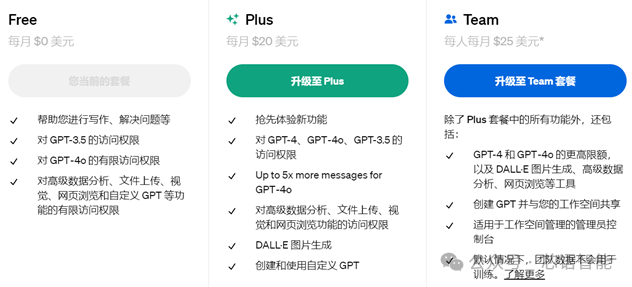

之前GPT-4的能力,听说可以免费使用了,抓紧体验一下世界顶级大模型。

原来免费套餐也是有对GPT-4o有限访问权限。

问一下,确认一下模型身份。

机会难得,找个难一点的问题来问。数据中心、高性能计算、人工智能、机器学习和存储等应用 需要高性能网卡,问下怎么设计高性能网卡。

问题1:想设计高性能网卡,请给出模块化设计方案:设计基于RoCEv2协议的高性能网卡,比如采用FPGA进行硬件加速,通过软硬件结合,考虑满足性能和提高开发进度,模块化设计分为如下几个模块,功能尽量解耦,方便并行开发。

答:设计一个基于FPGA进行硬件加速的RoCEv2 RDMA高性能网卡,可以通过模块化设计来实现,软硬件结合,提高性能和开发进度。以下是一个可能的模块化设计方案,每个模块的功能尽量解耦,以便于并行开发。

回答的还挺专业啊,像模像样。网卡方案分为几个模块,传输层协议引擎:处理RoCEv2协议的UDP/IP封装和解封装,错误处理和流量控制。队列对管理器:管理RDMA操作中的队列对,如发送队列(SQ)、接收队列(RQ)和完成队列(CQ)。内存管理单元:处理内存地址转换、访问权限验证和内存保护。网络接口和物理层:实现与物理以太网的连接,处理MAC和PHY层的功能。完整性和性能监控:监控网络和设备的性能,确保数据传输的完整性和正确性。管理配置:提供网卡的配置和管理功能,包括固件升级、参数设置等。安全模块:提供数据加密和完整性检验,确保安全通信。 再问的细致点试试? 问题2 软硬件结合分工,需要考虑开发进度要求,在满足性能和灵活性的条件下,软件和硬件功能方面怎么分配更优化呢? 答:在设计基于FPGA的硬件加速解决方案时,需要在性能和开发进度之间找到一个平衡点。软硬件结合的设计应当充分利用FPGA的并行处理能力,同时保持灵活性,便于软件层的更新和维护。以下是优化软硬件分配的一些建议:

1. 传输层协议引擎

- 硬件实现:

封装/解封装子模块:利用FPGA并行处理能力加速UDP/IP封装和解封装。

流量控制子模块:硬件实现拥塞控制以提高实时性和效率。

错误处理子模块:基本的错误检测和纠错可以硬件实现,提供低延迟的错误处理。

- 软件实现:

高级流量管理策略可以通过软件实现,便于调整和优化。

复杂的错误处理和恢复逻辑可以在软件中处理,以便于维护和更新。

2. 队列对管理器

- 硬件实现:

队列调度子模块:硬件实现基本的队列调度,确保低延迟。

队列状态监控子模块:硬件实时监控队列状态,提高响应速度。

- 软件实现:

高级调度策略和队列优化算法可以由软件实现,以提高灵活性。

非关键路径的状态监控和统计分析可以由软件处理。

3. 内存管理单元

- 硬件实现:

地址转换子模块:硬件实现虚拟到物理地址转换,确保高效。

权限验证子模块:硬件实现基本的访问权限验证,提高安全性和效率。

- 软件实现:

复杂的权限管理策略和动态调整可以通过软件实现,以增强灵活性。

内存保护策略可以由软件动态配置和调整。

4. 网络接口和物理层

- 硬件实现:

MAC层处理子模块:硬件实现以太网帧处理,确保低延迟和高吞吐量。

PHY层处理子模块:硬件处理物理层信号转换,确保稳定的物理连接。

- 软件实现:

- 配置和管理PHY层参数可以通过软件实现,以便于调试和维护。

5. 完整性和性能监控

- 硬件实现:

性能监控子模块:硬件实现实时性能监控,提供高精度的数据。

完整性检测子模块:硬件实现基本的数据完整性检查,提高实时性。

- 软件实现:

- 复杂的性能分析和数据处理由软件实现,便于灵活调整和优化。

- 长期统计和报告生成由软件处理。

6. 管理配置

- 软件实现:

固件管理子模块:软件实现固件升级和版本管理,提高灵活性。

配置管理子模块:软件实现各种参数设置和保存,便于更新和维护。

7. 安全模块

- 硬件实现:

数据加密子模块:硬件实现数据加密和解密,提供高性能的安全处理。

完整性检验子模块:硬件实现基本的完整性检验,提高实时性和效率。

- 软件实现:

复杂的加密策略和安全协议由软件实现,便于灵活调整和更新。

高级安全管理和策略配置由软件处理。

8. 日志与调试模块

- 软件实现:

日志记录子模块:软件实现系统日志记录,便于调试和维护。

调试接口子模块:软件实现调试接口,提供灵活的调试手段。

9. 兼容性和扩展模块

- 软件实现:

协议兼容子模块:软件实现各种协议兼容,便于灵活更新和维护。

扩展接口子模块:软件实现扩展接口,便于未来的功能扩展和升级。 通过以上分配,硬件模块主要承担实时性和高性能要求较高的功能,软件模块则负责复杂的逻辑处理和灵活的策略管理。这种分配可以确保开发进度的同时,充分利用FPGA的硬件加速能力,提高整体系统的性能和灵活性。

答3 :传输层协议引擎和网络接口及物理层之间的对接接口,我们需要考虑它们之间的数据流、控制信号和状态信号的交互。以下是详细分析:

数据信号

- 传输数据信号(Tx Data)

从传输层协议引擎到网络接口的传输数据。

通常为数据包的实际内容(例如以太网帧)。

- 接收数据信号(Rx Data)

从网络接口到传输层协议引擎的接收数据。

包括接收到的数据包(例如UDP/IP数据)。

控制信号

- 传输数据有效信号(Tx Data Valid)

传输层协议引擎通知网络接口有有效数据需要传输。

- 接收数据有效信号(Rx Data Valid)

网络接口通知传输层协议引擎接收到有效数据。

- 传输数据准备好信号(Tx Data Ready)

网络接口通知传输层协议引擎可以发送数据。

- 接收数据准备好信号(Rx Data Ready)

传输层协议引擎通知网络接口可以接收数据。

- 流量控制信号(Flow Control)

双方协调传输速率,防止数据丢失或缓冲区溢出。

状态信号

- 传输状态信号(Tx Status)

网络接口反馈传输状态,如传输成功、传输失败等。

- 接收状态信号(Rx Status)

传输层协议引擎反馈接收状态,如接收成功、校验错误等。

- 链路状态信号(Link Status)

网络接口反馈物理链路状态,如链路连接、链路断开等。

接口信号详细描述

- 数据信号

Tx_Data[WIDTH-1:0]:宽度根据实际数据宽度确定(如32位、64位等)。

Rx_Data[WIDTH-1:0]:同上,接收数据宽度。

- 控制信号

Tx_Data_Valid: 表示传输数据有效。

Rx_Data_Valid: 表示接收数据有效。

Tx_Data_Ready: 表示可以发送数据。

Rx_Data_Ready: 表示可以接收数据。

Flow_Control: 表示流量控制状态,如pause信号。

- 状态信号

Tx_Status[STATUS_WIDTH-1:0]: 传输状态信号,包含成功、失败、重试等信息。

Rx_Status[STATUS_WIDTH-1:0]: 接收状态信号,包含成功、错误、重试等信息。

Link_Status: 物理链路状态,如0表示断开,1表示连接。

接口信号示例

总结

通过上述分析,可以形成如下对接接口的设计方案:

- 数据信号(Tx_Data, Rx_Data):用于传输和接收数据。

- 控制信号(Tx_Data_Valid, Rx_Data_Valid, Tx_Data_Ready, Rx_Data_Ready, Flow_Control):用于控制数据传输和接收的有效性和准备状态。

- 状态信号(Tx_Status, Rx_Status, Link_Status):用于反馈传输、接收和链路状态。 这些信号可以通过标准的接口(如AXI4-Stream、Avalon-ST等)来实现,以确保传输层协议引擎与网络接口及物理层之间的高效、可靠通信。这些信号的定义和具体实现可以根据FPGA平台和实际需求进行调整和优化。